1. 今天谈一下信号完整性。

推荐书籍:李玉山老师翻译的《信号完整性分析》

信号完整性,就是将发送端信号准确完整的发送到接收端。

在此重点之重点就是掌握传输线的概念。在此抛砖引玉给提示一下。

我们在《

电路分析》中总是认为:同一导线上任意两点电压和电流均相等。

现在假设有一个1GHz的正弦波电信号在1m长的双绞线上传输,请问双绞线上每一点电压相等吗?

由于1GHz电信号波长近似为30厘米(暂且认为双绞线塑料层表皮相对介电常数为1,下面类同),当它在1m长的线上传播时,需要接近3个波长长度才能从始端传到末端。大脑想一下水中波纹的传播情况,显然线上不可能每点电压相等,而是像波纹一样分布。

因此,我们不能用电路(集总参数)的理论去分析这种情况,而要用新的不同于电路的理论,即传输线(分布参数)理论分析问题。

此处需要说明:一般线长小于波长1/20时,认为线上任意两点电压相等,可以使用电路理论分析问题,否则使用传输线理论。

为了更好的说明传输线理论,再想象一种情形。

在1m长的双绞线中,始端(源端)发出信号1ns后,电压和电流是怎样分布的?在速度是3*10^8 m/s的情况下,仅仅前进了30cm,并没有到达距离1m远的负载端,有没有电流?有的话电流是哪来的?

今天先说到这,有空继续更新。下面再提几个关键词最好了解一下。

特征阻抗,反射系数,源端匹配,末端匹配,过冲(振铃),CMOS电路输入和输出阻抗特性,串扰,带状线,微带线,趋肤效应,S参数,3w原则等。

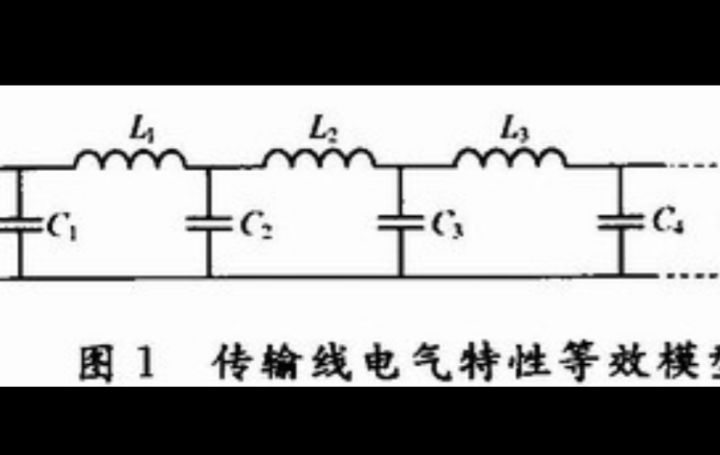

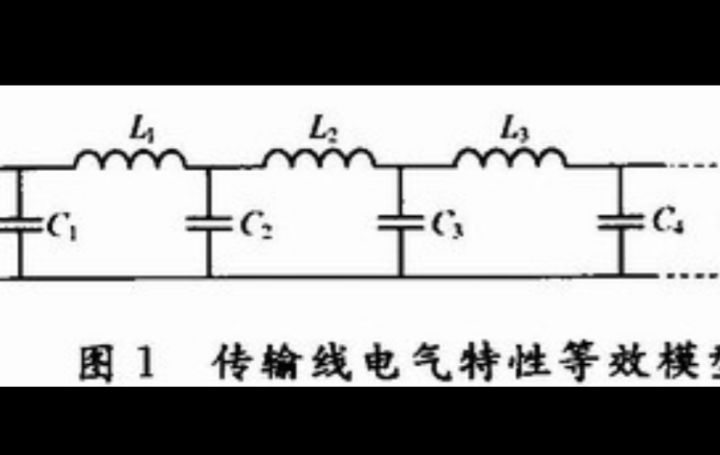

现在需要引入传输线的电路等效模型。既然电路观点认为同一导线上任意两点电流电压相等,那么我们就可以将传输线进行切割,认为是多个一小段一小段的线缆串联连接,当将每一小段分的足够小时,每一小段上电压和电流就是相等的。因此我们就可以在每一个小段上使用电路理论进行分析了。

电路等效模型如下

为了能够看明白电路等效模型,先分析一下电感和电容本质

电容本质是表示电场的存在

电感本质是表示磁场的存在

电信号传输过程实际是电磁波的传输,电磁波既有电场也有磁场,有电场就有电容,有磁场就有电感。因此,我们看到了传输线电路模型是电感加电容。

当交流信号源加载在传输线一侧时,通过电感和电容便有了电流,无需走到负载端即可在返回路径上形成电流。实际上,电流是磁场的旋度源,电荷是电场的散度源,两者同时存在正好符合了电磁波中电场和磁场的传输条件。

走了电压和电流,那么电压除以电流就是阻抗,在此便是传输线的特征阻抗。具体特征阻抗推导请看

https://www.zhihu.com/question/2 ... p;utm_medium=social]

有了这些知识,我们就可以讨论反射系数和阻抗匹配了。

正如上面所述,传输线中电压V和电流I符合关系

V/I=Z0

其中Z0为传输线的特征阻抗

现在传输线以这个关系将电磁场能量传输了出来,过了一段时间到负载端了。负载阻抗Zl,负载说:对不起,我收下的能量必须符合关系

V/I=Zl

天哪,传输线已经把能量以自己的关系送出来了,但是负载可能不能照单全收,怎么办呢?

传输线只好把一部分能量在返回去,返回去的能量就是反射。如果传输线特征阻抗和负载阻抗相等,就不存在能量返回,就是末端匹配。

信号完整性就说这么多,希望能帮到大家。最后,提一个非常非常重要的概念就是:返回路径。真的很重要,希望大家布线时,时时处处想着她。她就是

PCB中的女神!

今天先说到这

_____

今天开始说一下

电源完整性20171229

2、电源完整性

电源完整性从两个角度讨论(1)电源完整性产生的原因(2)怎样解决电源完整性

(1)电源完整性产生的原因

两个原因①电源回路存在电感②负载电流是瞬态变化的

先说回路电感,请参考

https://www.zhihu.com/question/5 ... p;utm_medium=social

就是,存在回路就存在磁场,有磁场就有电感

再说负载电流的瞬态变化

现在的数字电路都是CMOS工艺,CMOS器件的静态漏电流很小,但是在电平翻转时的动态电流很大。动态电流包括两部分,一部分是由于输入电压从高电平到低电平或者从低电平到高电平时,会存在中间电平的瞬间,此时上下两个管子均工作在放大区,有经过两个管子从电源到地的电流。另外一部分是由于负载端的电容充放电导致的电流。

因此,在器件工作时钟的上升沿和下降沿会存在较大的动态电流,每次翻转器件数量不同电流也不同。一般除时钟沿外的其他时刻仅消耗漏电流。

瞬态电流经过电流回路电感是有压降,因此出现芯片处的电压不等于电源芯片输出端电压的情况,这便是电源完整性问题的根源。

今天先到这

(2)怎样解决电源完整性

在电源完整性的原因一部分中,我们知道由于电源回路电感的存在,导致电源供应电压不等于芯片用电处电压。

那么怎样才能解决这个问题?唯有减小回路面积,以减小回路电感,进而减小供电线路压降。

但是,整个芯片那么多的电源管脚,怎样可以保证每一个供电管脚均有较小的回路面积呢?

这时候别忘记电容,电容的本事就是储存电荷,每一个电容都可以看做一个小的临时电源,给每一个电源管脚分配一个电容就可以看做每一个管脚分配一个电源,我们就可以减小每一个电源管脚的电源供电回路了。

电容是怎样工作的?

芯片在时钟上升沿和下降沿翻转需要的电流,临时从电容中抽取。在时钟高电平和低电平阶段期间,电容从电源中补充能量,迎接下一次的电流消耗。

我们参观故宫或者古代建筑时,会发现外面都有一口大缸灌满了水,它的作用就是用来应急救火用的。它的作用和咱们的电容是不是很像?

那么需要多大的电容可以满足要求呢?

我们从两个角度考虑

①时域分析

假设芯片瞬间最大电流i,电压允许波动Δv,那么从电容放出电荷等于芯片消耗的电荷,即:

C(Δv)=i(Δt)

此处的(Δt)怎么取?我们知道上升沿和下降沿均消耗电流,所以取芯片工作周期的一半即可

②频域阻抗

时域角度说明了总电容容量,但是对一些细节没有描述,下面我们再从频域考虑电源完整性问题。

频域怎么看问题呢?

我们将频率为w0的正弦电压u加到电源上,电源会输出一个同样频率的电流i,那么就得到频率w0时的电源阻抗

Z(w=w0)=u╱i

同样,芯片消耗的的特定频率w0的电流i(w=w0)流经同样的回路,将感受到同样的回路阻抗Z(w=w0),此时将产生一个压降

U(w=w0)=i(w=w0)×Z(w=w0)

但是,实际上我们并不能得到芯片在电源上对电压的纹波频域特性要求和电流的频域特性

怎么办?怎么办?难道频域分析半天没有用了?

不,这些难不倒我们的工程师

我们使用最坏情况进行分析

假如允许最大纹波电压(Δu)max,瞬间消耗最大电流imax,那么令

U(w)=(Δu)max

i(w)=imax

此时,可以算出Z(w)=U(w)╱i(w)

在设计过程中,只要频域阻抗低于Z(w)就可以保证,电源纹波满足芯片要求了

频域设计方法由于使用了最坏情况分析法,所以设计裕度非常大。

实际使用频域阻抗设计要求非常严格,有时是不可能满足的。这个方法给我们提供了一个角度看问题,具体设计出来还得进行测试。

作者:Jld

链接:

https://www.zhihu.com/question/263949416/answer/275304418

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

1

1

举报

举报