利用FPGA或CPLD进行电路设计的流程由以下几个普通步骤组成:设计入口、设计确认、设计汇编和器件编程。设计入口阶段由捕获设计组成,不是通过利用电脑辅助设计工具创建图形化原理图,就是通过利用Verilog或VHDL等硬件描述语言来描述电路。在捕获设计之后,通过使用电路模拟来检验正确的功能性和性能加以验证。如果电路没有达到要求性能,则工程师师就回到设计入口阶段对设计加以调整,然后重复设计验证阶段。设计入口和设计验证步骤可能反复多次,才能使设计能够满足全部功能和性能要求。在获得令人满意的设计之后,工程师使用FPGA或CPLD器件供应商提供的软件对设计进行“汇编”,用于对实现设计的器件进行配置。编译形成的文档被下载到FPGA或CPLD,并给内部逻辑器件编程使之具有正确的功能性。

为现场可编程器件供电

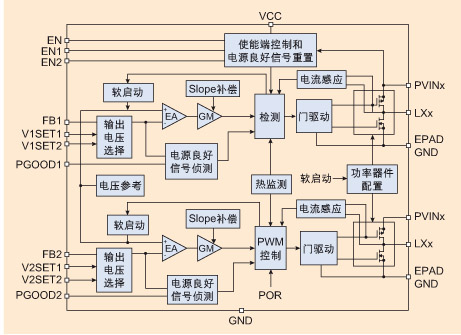

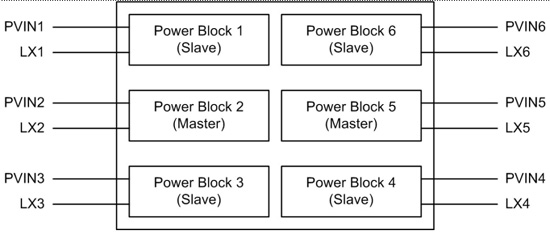

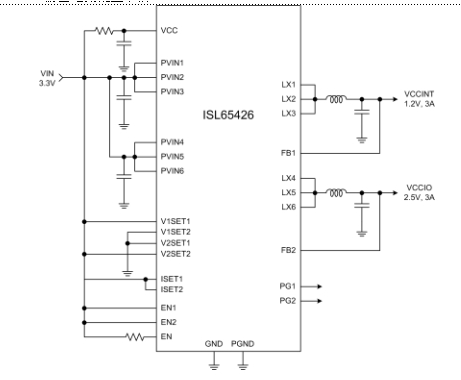

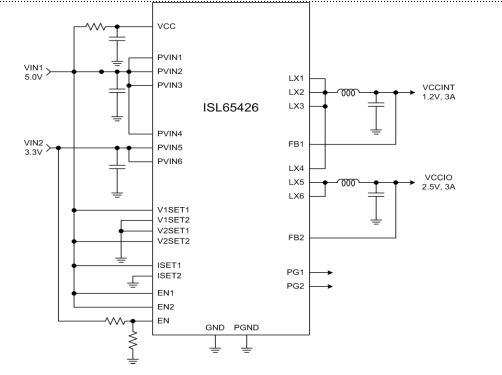

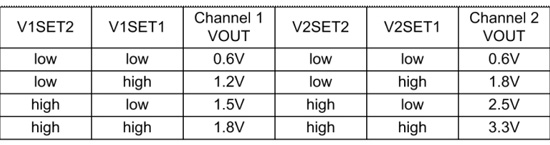

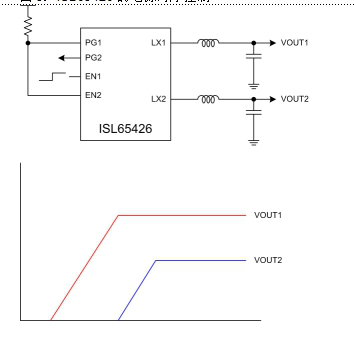

通常利用三个基本电源轨对FPGA供电:核心电源轨、I/O电源轨和辅助电源轨。其中每个电源轨都具有不同的负载电源要求。核心电源轨VCCINT,向器件的内部逻辑供电,通常具有最严格的电流要求。对上几代的FPGA,VCCINT上面的电压可能高达3.3V,而目前的器件则低至1.2V。I/O电源轨 VCCIO为FPGA的输入/输出模块供电。该电源轨上的电压可能是1.5V、1.8V、2.5V或3.3V,取决于所采用的I/O标准。具体选择什么 I/O标准,受FPGA将与之通讯的器件左右。辅助电源轨VCCAUX用于为FPGA上面的数字时钟管理器和JTAG I/O供电,电压通常是2.5V或3.3V。

可变的功率要求

通过重复上述的设计汇编和下载步骤,工程师可以随时改变FPGA或CPLD的编程和配置。FPGA根据新设计的要求进行重新配置没有次数限制。不需改变电路板上的线迹、不需要更换元件、不需要重新焊接,因此可以非常迅速及方便地解决故障和进行调整。另外,可以为给定的设计添加功能和特点,而对于物理设计并无影响。这使现场可编程器件获得巨大优势,可以作为复杂的数字系统的实现手段。

但是,获得这样的灵活性也需要付出代价。FPGA的电源要求,具体而言就是它要消耗的电源电流,与设计的复杂程度成正比。对FPGA进行重新配置,使其具有新的功能,将改变对为其供电的电源系统的要求。FPGA被使用的程度越高,它需要的电流就越大。电流需求也会随着时钟频率的上升而增加,因此FPGA速度越快,它消耗的功率越大。因此,FPGA功能的改变将决定电源设计的改变。

利用FPGA或CPLD进行电路设计的流程由以下几个普通步骤组成:设计入口、设计确认、设计汇编和器件编程。设计入口阶段由捕获设计组成,不是通过利用电脑辅助设计工具创建图形化原理图,就是通过利用Verilog或VHDL等硬件描述语言来描述电路。在捕获设计之后,通过使用电路模拟来检验正确的功能性和性能加以验证。如果电路没有达到要求性能,则工程师师就回到设计入口阶段对设计加以调整,然后重复设计验证阶段。设计入口和设计验证步骤可能反复多次,才能使设计能够满足全部功能和性能要求。在获得令人满意的设计之后,工程师使用FPGA或CPLD器件供应商提供的软件对设计进行“汇编”,用于对实现设计的器件进行配置。编译形成的文档被下载到FPGA或CPLD,并给内部逻辑器件编程使之具有正确的功能性。

为现场可编程器件供电

通常利用三个基本电源轨对FPGA供电:核心电源轨、I/O电源轨和辅助电源轨。其中每个电源轨都具有不同的负载电源要求。核心电源轨VCCINT,向器件的内部逻辑供电,通常具有最严格的电流要求。对上几代的FPGA,VCCINT上面的电压可能高达3.3V,而目前的器件则低至1.2V。I/O电源轨 VCCIO为FPGA的输入/输出模块供电。该电源轨上的电压可能是1.5V、1.8V、2.5V或3.3V,取决于所采用的I/O标准。具体选择什么 I/O标准,受FPGA将与之通讯的器件左右。辅助电源轨VCCAUX用于为FPGA上面的数字时钟管理器和JTAG I/O供电,电压通常是2.5V或3.3V。

可变的功率要求

通过重复上述的设计汇编和下载步骤,工程师可以随时改变FPGA或CPLD的编程和配置。FPGA根据新设计的要求进行重新配置没有次数限制。不需改变电路板上的线迹、不需要更换元件、不需要重新焊接,因此可以非常迅速及方便地解决故障和进行调整。另外,可以为给定的设计添加功能和特点,而对于物理设计并无影响。这使现场可编程器件获得巨大优势,可以作为复杂的数字系统的实现手段。

但是,获得这样的灵活性也需要付出代价。FPGA的电源要求,具体而言就是它要消耗的电源电流,与设计的复杂程度成正比。对FPGA进行重新配置,使其具有新的功能,将改变对为其供电的电源系统的要求。FPGA被使用的程度越高,它需要的电流就越大。电流需求也会随着时钟频率的上升而增加,因此FPGA速度越快,它消耗的功率越大。因此,FPGA功能的改变将决定电源设计的改变。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报