RFID电子标签已经成为21世纪全球自动识别技术发展的主要方向。目前,RFID已经得到了广泛应用,且有国际标准ISO10536,ISO14443,ISO15693,ISO18000,EPC Global等几种。其中,ISO18000-6C属于超高频射频识别技术标准,它融合了EPC C1G2标准。该标准的特点是速度快,可以同时读取的标签数量多,理论上能读到1 000多个标签;功能强,具有多种写保护方式;安全性强。

在我国,由于射频识别技术起步较晚,应用的领域不是很广,主要的应用是基于中低频的应用,包括车辆管理、门禁管理等。目前,超高频射频识别技术及其应用在我国正处于初级发展阶段,国内目前还没有成熟的超高频电子标签芯片设计技术。

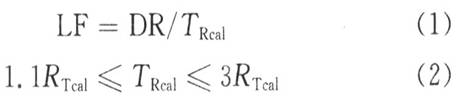

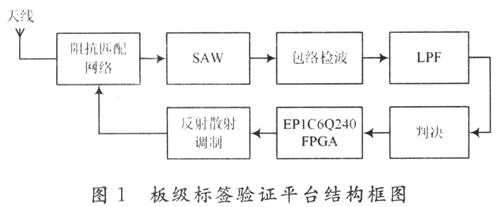

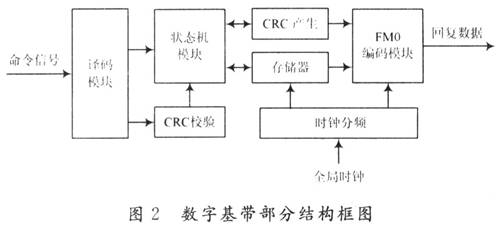

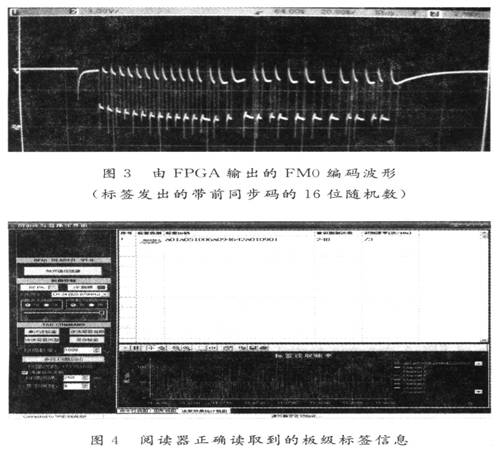

在此,首先介绍电子标签的工作原理及ISO18000-6C标准,并根据ISO18000-6C标准,设计了实现超高频电子标签验证平台的整体电路。重点讨论基于EP1C6Q240FPGA的数字基带部分设计与实现。最后给出了该平台的测试结果,验证了平台设计的正确性和可靠性。

1 电子标签的工作原理

射频识别系统通常由读写器(Reader)和射频标签(RFID Tag)构成。附着在待识别物体上的射频标签内存有约定格式的电子数据,作为待识别物品的标识性信息。读写器可无接触地读出标签中所存的电子数据或者将信息写入标签,从而实现对各类物体的自动识别和管理。读写器与射频标签按照约定的通信协议采用先进的射频技术互相通信,其基本通信过程如下。

(1)读写器作用范围内的标签接收读写器发送的载波能量,上电复位;

(2)标签接收读写器发送的命令并进行操作;

(3)读写器发出选择和盘存命令对标签进行识别,选定单个标签进行通信,其余标签暂时处于休眠状态;

(4)被识别的标签执行读写器发送的访问命令,并通过反向散射调制方式向读写器发送数据信息,进入睡眠状态,此后不再对读写器应答;

(5)读写器对余下标签继续搜索,重复(3),(4)分别唤醒单个标签进行读取。直至识别出所有标签。

标签向读写器传送数据是通过反向散射调制技术,对于无源电子标签,其本身没有足够的发射能量,所以通过改变天线的匹配阻抗控制天线的反射强弱,阻抗不匹配时天线反射率很大,阻抗匹配时天线反射率很小,以此来表示输出信号的有无。

。

RFID电子标签已经成为21世纪全球自动识别技术发展的主要方向。目前,RFID已经得到了广泛应用,且有国际标准ISO10536,ISO14443,ISO15693,ISO18000,EPC Global等几种。其中,ISO18000-6C属于超高频射频识别技术标准,它融合了EPC C1G2标准。该标准的特点是速度快,可以同时读取的标签数量多,理论上能读到1 000多个标签;功能强,具有多种写保护方式;安全性强。

在我国,由于射频识别技术起步较晚,应用的领域不是很广,主要的应用是基于中低频的应用,包括车辆管理、门禁管理等。目前,超高频射频识别技术及其应用在我国正处于初级发展阶段,国内目前还没有成熟的超高频电子标签芯片设计技术。

在此,首先介绍电子标签的工作原理及ISO18000-6C标准,并根据ISO18000-6C标准,设计了实现超高频电子标签验证平台的整体电路。重点讨论基于EP1C6Q240FPGA的数字基带部分设计与实现。最后给出了该平台的测试结果,验证了平台设计的正确性和可靠性。

1 电子标签的工作原理

射频识别系统通常由读写器(Reader)和射频标签(RFID Tag)构成。附着在待识别物体上的射频标签内存有约定格式的电子数据,作为待识别物品的标识性信息。读写器可无接触地读出标签中所存的电子数据或者将信息写入标签,从而实现对各类物体的自动识别和管理。读写器与射频标签按照约定的通信协议采用先进的射频技术互相通信,其基本通信过程如下。

(1)读写器作用范围内的标签接收读写器发送的载波能量,上电复位;

(2)标签接收读写器发送的命令并进行操作;

(3)读写器发出选择和盘存命令对标签进行识别,选定单个标签进行通信,其余标签暂时处于休眠状态;

(4)被识别的标签执行读写器发送的访问命令,并通过反向散射调制方式向读写器发送数据信息,进入睡眠状态,此后不再对读写器应答;

(5)读写器对余下标签继续搜索,重复(3),(4)分别唤醒单个标签进行读取。直至识别出所有标签。

标签向读写器传送数据是通过反向散射调制技术,对于无源电子标签,其本身没有足够的发射能量,所以通过改变天线的匹配阻抗控制天线的反射强弱,阻抗不匹配时天线反射率很大,阻抗匹配时天线反射率很小,以此来表示输出信号的有无。

。

举报

举报

举报

举报

举报

举报

举报

举报