3 结束语

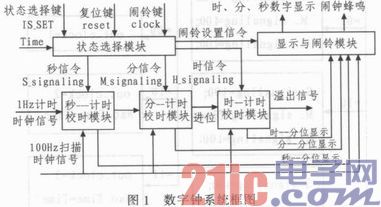

在QuartusⅡ软件开发平台上,采用“自顶向下设计,自底向上实现”的方法完成了数字钟的设计与实现。其基本过程如下:1)完成数字钟的总体设计;2)完成各个底层模块的设计和波形仿真:底层模块采用VHDL语言编写,在编译和仿真成功后,对其进行封装;3)完成数字钟的顶层电路设计:根据数字钟的系统框图(图1)在QuartusⅡ中采用电路原理图方式,调用封装好的底层模块,完成顶层电路图的设计;4)对顶层电路进行编译和仿真,结果表明仿真波形符合设计要求;5)进行引脚分配,再编译后,将下载文件下载到FPGA开发板中进行验证和调试。测试结果表明数码管能正确的显示计时时间, 能通过按键调整时间,能实现整点报时,完全符合设计要求。

3 结束语

在QuartusⅡ软件开发平台上,采用“自顶向下设计,自底向上实现”的方法完成了数字钟的设计与实现。其基本过程如下:1)完成数字钟的总体设计;2)完成各个底层模块的设计和波形仿真:底层模块采用VHDL语言编写,在编译和仿真成功后,对其进行封装;3)完成数字钟的顶层电路设计:根据数字钟的系统框图(图1)在QuartusⅡ中采用电路原理图方式,调用封装好的底层模块,完成顶层电路图的设计;4)对顶层电路进行编译和仿真,结果表明仿真波形符合设计要求;5)进行引脚分配,再编译后,将下载文件下载到FPGA开发板中进行验证和调试。测试结果表明数码管能正确的显示计时时间, 能通过按键调整时间,能实现整点报时,完全符合设计要求。

举报

举报

举报

举报

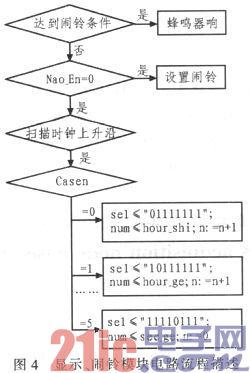

2.2 计时校时模块设计

2.2 计时校时模块设计 计时校时模块的电路描述如图3所示,具体说明如下:每当扫描时钟上升沿时,启动进程,并根据信令signaling执行不同操作,1)当signaling

计时校时模块的电路描述如图3所示,具体说明如下:每当扫描时钟上升沿时,启动进程,并根据信令signaling执行不同操作,1)当signaling

举报

举报

举报

举报