目前,数字通信系统正向高速全数字化方向发展。在全数字接收机定时同步中,主要包括两个关键点:定时误差估计和定时控制。传统的定时同步方法中一般直接调节本地采样时钟以达到采样最佳的效果,而在全数字接收机中,本地采样时钟不变,通过计算定时误差控制产生重采样时钟达到最佳采样。通过产生重采样时钟达到定时同步的方法常用的有Gardner算法和数字滤波平方法。

其中,cn为发送的符号数据;g(t):gT(t)×gR(t)为系统脉冲响应;gT(t)为发送端成型滤波器的脉冲响应;gR(t)为接收端匹配滤波器的脉冲响应;T为符号周期;s(t)为慢变的采样时间误差;B(t)为载波相差,这里不考虑载波相差,即B(t)=0,n(t)为高斯噪声,n(t)~N(0,2δ2),其同相分量和正交分量的方差均为δ2。

其中,cn为发送的符号数据;g(t):gT(t)×gR(t)为系统脉冲响应;gT(t)为发送端成型滤波器的脉冲响应;gR(t)为接收端匹配滤波器的脉冲响应;T为符号周期;s(t)为慢变的采样时间误差;B(t)为载波相差,这里不考虑载波相差,即B(t)=0,n(t)为高斯噪声,n(t)~N(0,2δ2),其同相分量和正交分量的方差均为δ2。 式中求出的定时误差

式中求出的定时误差 为ε的无偏估计。

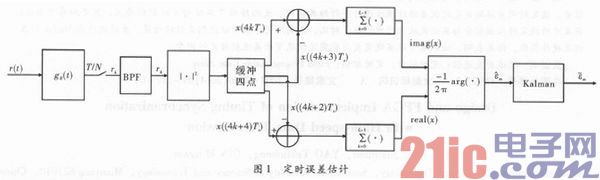

为ε的无偏估计。 其中,匹配滤波之后,加入一个中心频率为1/2T,带宽为α/T的带通滤波器,用来滤除带外噪声,并在误差求出之后加入一个卡尔曼滤波器,用以对结果进行平滑。

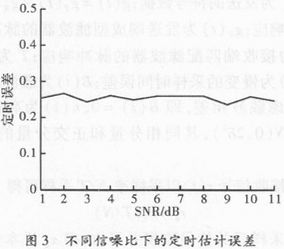

其中,匹配滤波之后,加入一个中心频率为1/2T,带宽为α/T的带通滤波器,用来滤除带外噪声,并在误差求出之后加入一个卡尔曼滤波器,用以对结果进行平滑。 预设定时误差为1/4,在不同输入信噪比情况下验证定时误差估计的准确性,如图3所示。定时误差并行算法结构能够正确地估计定时误差。

预设定时误差为1/4,在不同输入信噪比情况下验证定时误差估计的准确性,如图3所示。定时误差并行算法结构能够正确地估计定时误差。

举报

举报

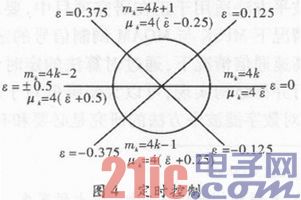

Gardner定时控制方法和新控制方法分别为两种定时控制方法在码速率为300 MHz,采样率为1.2 GHz,时偏为0.25T,SNR为15 dB时的星座图。从星座图可明显看出,新控制方法效果更好,星座图更加收敛。

Gardner定时控制方法和新控制方法分别为两种定时控制方法在码速率为300 MHz,采样率为1.2 GHz,时偏为0.25T,SNR为15 dB时的星座图。从星座图可明显看出,新控制方法效果更好,星座图更加收敛。 4 Matlab仿真

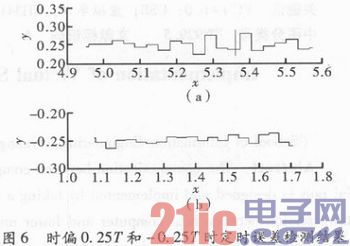

4 Matlab仿真 当时偏设为0.25T和-0.25T时,环路定时误差检测结果分别如图6(a)和图6(b)所示。通过图8可以看出误差检测结果是可信的。

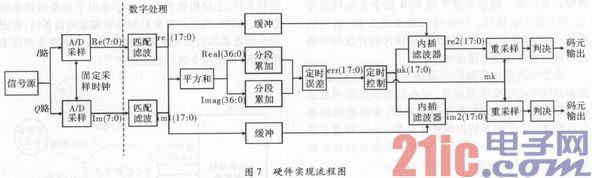

当时偏设为0.25T和-0.25T时,环路定时误差检测结果分别如图6(a)和图6(b)所示。通过图8可以看出误差检测结果是可信的。  信号源部分使用信号发生器产生300 MHz的BPSK信号,A/D采样率为1.2 GHz,A/D直接对基带信号以4倍的符号率采样,匹配滤波的滚降系数为0.5,数字处理部分采用Xilinx公司的Virtex-4系列FPGA芯片。算法实现消耗8%的Slices以及14%的DSP48s。

信号源部分使用信号发生器产生300 MHz的BPSK信号,A/D采样率为1.2 GHz,A/D直接对基带信号以4倍的符号率采样,匹配滤波的滚降系数为0.5,数字处理部分采用Xilinx公司的Virtex-4系列FPGA芯片。算法实现消耗8%的Slices以及14%的DSP48s。

举报

举报

举报

举报

更多回帖