4 结论

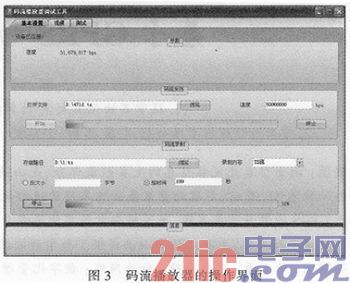

码流播放器是USB供电,无需额外电源,轻巧方便携带;能轻松捕捉,播放,录制和分析码流;精确控制码流发送速度;全双工,同时进行码流的发送和接收。

用户界面简单明了。发送时选择发送文件,再输入发送速度,点击开始即可;接收时选择存储路径和录制内容,再选择录制方式,点击开始。同时,用户界面还能实时接收到FPGA分析得到的各种码流参数信息。目前,本文所介绍的码流播放器已进入稳定性测试阶段,各项功能也在不断完善和优化中。

码流播放器的电路板仅为6 mm*9 mm,小巧轻便,方便携带;操作简单,界面友好;因为设计时严格控制成本,价格低廉,性价比高,是数字电视专业人员理想的测试工具。

4 结论

码流播放器是USB供电,无需额外电源,轻巧方便携带;能轻松捕捉,播放,录制和分析码流;精确控制码流发送速度;全双工,同时进行码流的发送和接收。

用户界面简单明了。发送时选择发送文件,再输入发送速度,点击开始即可;接收时选择存储路径和录制内容,再选择录制方式,点击开始。同时,用户界面还能实时接收到FPGA分析得到的各种码流参数信息。目前,本文所介绍的码流播放器已进入稳定性测试阶段,各项功能也在不断完善和优化中。

码流播放器的电路板仅为6 mm*9 mm,小巧轻便,方便携带;操作简单,界面友好;因为设计时严格控制成本,价格低廉,性价比高,是数字电视专业人员理想的测试工具。

举报

举报

举报

举报

举报

举报

举报

举报