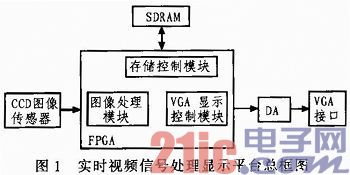

一般视频处理后的实时显示终端不能脱离PC机的束缚,而且数字图像传感器输出的图像帧率也比较低,分辨率也随着

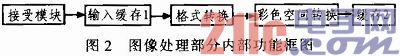

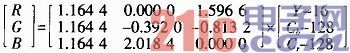

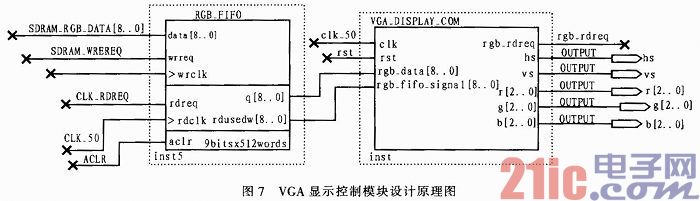

半导体行业的发展有了很大的提高,因此为了输出的图像能直接在VGA显示器上显示,需要对图像进行帧率提升、彩色空间转换等处理。

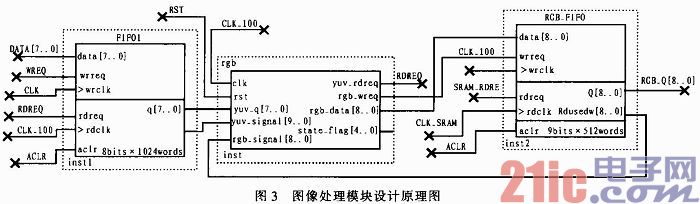

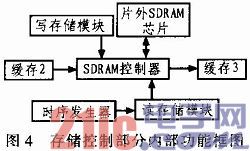

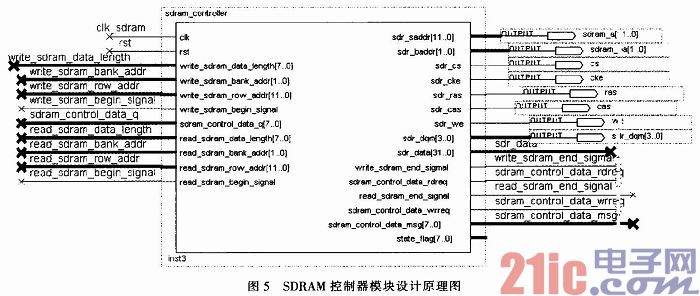

FPGA器件具有可重复编程的灵活性以及并行处理能力,并且随着微处理器、专用硬件单元、DSP算法以及IP核的嵌入使其功能越来越强大。本系统的设计是基于Altera公司的EP2S60系列的

开发板,板上集成两片SDRAM存储芯片、视频输入接口和VGA输出接口。

举报

举报

举报

举报

举报

举报