2. 设计特点

与ASIC相比,FPGA的特点是功能强,设计灵活,随时升级,工作成果可以积累,NRE低,但是芯片价格比ASIC贵,所以必须找到一个可以达到价格平衡的应用领域,我们根据这几年智能手机和3G网络发展迅猛的情况,参考电信运营商第一代全球眼的技术指标,直接把设计指标定位在码流小于512kbps和分辨率为1280x720x25fps,目前在市面上可以实现这些指标的摄像机几乎没有,这是FPGA的好机会。

512kbps的码流限制主要是考虑到ADSL和家庭光端机的上传能力,而且也能利用3G上传视频,减少了智能手机的码流下载压力;1280x720是智能手机的主流分辨率,自然需要相应的视频源,如果显示D1或CIF,效果肯定不理想。

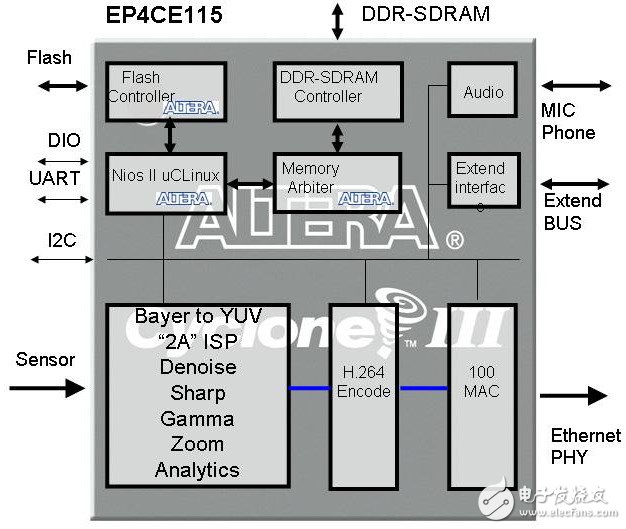

我 们的目标是做一个可以直接用于生产的参考设计,除了设计指标先进,我们还要考虑价格和实用,所以我们选择了低成本的CYCLONE IV系列,另外也实现了一般网络摄像机的全部功能,如H.264压缩、720p25帧三码流、双向语音、重要区域和隐私区域的定义、智能分析、移动检测、 声音侦测、POE供电等;

3. 实现高清低码流H.264摄像机SoC的关键

一般来说,1280×720×25fps的码流在2Mbps左右,如何降低码流?除了使用mail profile with cabac的H.264编码器外,还需要对视频图像进行分析,而且要在帧率、分辨率、视频质量等方面权衡折中,在512kbps码流下获得最好的视频效果,为了达到这样的目的,需要复杂灵活的控制,FPGA可以满足这样的需求。

2. 设计特点

与ASIC相比,FPGA的特点是功能强,设计灵活,随时升级,工作成果可以积累,NRE低,但是芯片价格比ASIC贵,所以必须找到一个可以达到价格平衡的应用领域,我们根据这几年智能手机和3G网络发展迅猛的情况,参考电信运营商第一代全球眼的技术指标,直接把设计指标定位在码流小于512kbps和分辨率为1280x720x25fps,目前在市面上可以实现这些指标的摄像机几乎没有,这是FPGA的好机会。

512kbps的码流限制主要是考虑到ADSL和家庭光端机的上传能力,而且也能利用3G上传视频,减少了智能手机的码流下载压力;1280x720是智能手机的主流分辨率,自然需要相应的视频源,如果显示D1或CIF,效果肯定不理想。

我 们的目标是做一个可以直接用于生产的参考设计,除了设计指标先进,我们还要考虑价格和实用,所以我们选择了低成本的CYCLONE IV系列,另外也实现了一般网络摄像机的全部功能,如H.264压缩、720p25帧三码流、双向语音、重要区域和隐私区域的定义、智能分析、移动检测、 声音侦测、POE供电等;

3. 实现高清低码流H.264摄像机SoC的关键

一般来说,1280×720×25fps的码流在2Mbps左右,如何降低码流?除了使用mail profile with cabac的H.264编码器外,还需要对视频图像进行分析,而且要在帧率、分辨率、视频质量等方面权衡折中,在512kbps码流下获得最好的视频效果,为了达到这样的目的,需要复杂灵活的控制,FPGA可以满足这样的需求。

举报

举报

举报

举报

举报

举报

举报

举报