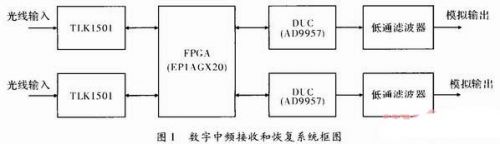

直接数字频率合成(Direct Digital Synthesizer,DDS)作为一种先进的信号产生技术,与传统的频率合成技术相比,DDS具有分辨率高、转换速度快、功耗低和成本低等优点,经过40年的发展,已被广泛用于数字信号处理、软件无线电等领域。在现在的雷达系统中,高速高宽带是现行的趋势,传统的并行传输技术由于存在码间串扰、串音干扰和直流偏移等缺点,难以满足高速高带宽的传输要求。目前国内外有关雷达高速宽带信号接收和恢复技术的研究很广泛,多采用软硬件相结合的设计方式,系统灵活,同时满足信号实时输出的要求。

举报

举报

举报

举报

举报

举报

举报

举报

更多回帖