在设计时,充分抓住异步数据的特征进行设计:起始位为低电平、停止位为高电平、每帧数据帧结构相同。根据异步数据这些特征就可设计出以下相应程序:

process(clk16x,start) --产生clk1x时钟进程

begin

if start=’0’ then

q<="0001";

elsif clk16x’event and clk16x=’1’

then

q<=q+1;

end if;

end procESS ;

clk1x<=q(3);

process(clk16x,i,serialin,rst) --起始位检测进程

begin

if rst=’1’ then

start<=’0’;

elsif rising_edge(clk16x) then if serialin=’0’ then

start<=’1’ ;

elsif over=’0’ then

start<=’1’;

else start<=’0’;

end if;

end if;

end process;

process(clk1x,serialin,i,rst) --读数据进程

begin

if rst=’1’ then

buff<= (others => ’1’);

Dout_P<= (others => ’1’);

i<=0;

over<=’1’;

elsif rising_edge(clk1x) then

if i<>

buff21<=serialin;

i<=i+1;

over<=’0’; else

i<=0;

over<=’1’;

Dout_P<=buff;

end if;

end if;

end process ;

本设计采用VHDL硬件描述语言来进行描述。clk16x为16倍频采样时钟,clk1x是检测到真正起始位后由clk16x时钟分频产生的采样时钟,start为开始接收数据信号(接收数据期间为高电平)、serialin为异步数据输入端口。平常,接收器按clk16x时钟上升采样serialin。当采样时钟检测到低电平时输出一个高电平给start信号,clk1x分频计数器启动。如果连续采集8个脉冲都为低电平(起始位之半),即确定该低电平为起始位,输出一个低电平给接收数据完信号over(接收数据期间为低电平,接收完数据为高电平),over信号在低电平检测共同作用下保持start为高电平。start长时间保持高电平(8个clk16周期T)产生clk1x时钟。反之判别为假起始位,over仍然为高电平,start却变为低电平,clk1x分频计数器复位,一直等到下次检测serialin为低电平才重新启动。可见,只有确定了起始位,clk1x时钟才会产生,否则不产生。而clk16x时钟始终存在,保证不会错过每次接收线上的数据采样。

结语

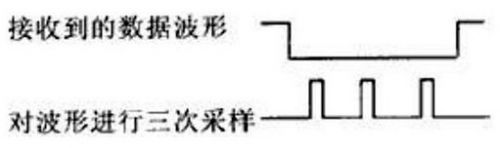

按常规的16倍频采样方法接收异步数据,其抗干扰性、移植性等都优于3倍频采样方法。实际应用表明,提高采样倍数,接收准确性相应提高;在一定范围内,提高数据波特率不会影响接收准确性。

在设计时,充分抓住异步数据的特征进行设计:起始位为低电平、停止位为高电平、每帧数据帧结构相同。根据异步数据这些特征就可设计出以下相应程序:

process(clk16x,start) --产生clk1x时钟进程

begin

if start=’0’ then

q<="0001";

elsif clk16x’event and clk16x=’1’

then

q<=q+1;

end if;

end procESS ;

clk1x<=q(3);

process(clk16x,i,serialin,rst) --起始位检测进程

begin

if rst=’1’ then

start<=’0’;

elsif rising_edge(clk16x) then if serialin=’0’ then

start<=’1’ ;

elsif over=’0’ then

start<=’1’;

else start<=’0’;

end if;

end if;

end process;

process(clk1x,serialin,i,rst) --读数据进程

begin

if rst=’1’ then

buff<= (others => ’1’);

Dout_P<= (others => ’1’);

i<=0;

over<=’1’;

elsif rising_edge(clk1x) then

if i<>

buff21<=serialin;

i<=i+1;

over<=’0’; else

i<=0;

over<=’1’;

Dout_P<=buff;

end if;

end if;

end process ;

本设计采用VHDL硬件描述语言来进行描述。clk16x为16倍频采样时钟,clk1x是检测到真正起始位后由clk16x时钟分频产生的采样时钟,start为开始接收数据信号(接收数据期间为高电平)、serialin为异步数据输入端口。平常,接收器按clk16x时钟上升采样serialin。当采样时钟检测到低电平时输出一个高电平给start信号,clk1x分频计数器启动。如果连续采集8个脉冲都为低电平(起始位之半),即确定该低电平为起始位,输出一个低电平给接收数据完信号over(接收数据期间为低电平,接收完数据为高电平),over信号在低电平检测共同作用下保持start为高电平。start长时间保持高电平(8个clk16周期T)产生clk1x时钟。反之判别为假起始位,over仍然为高电平,start却变为低电平,clk1x分频计数器复位,一直等到下次检测serialin为低电平才重新启动。可见,只有确定了起始位,clk1x时钟才会产生,否则不产生。而clk16x时钟始终存在,保证不会错过每次接收线上的数据采样。

结语

按常规的16倍频采样方法接收异步数据,其抗干扰性、移植性等都优于3倍频采样方法。实际应用表明,提高采样倍数,接收准确性相应提高;在一定范围内,提高数据波特率不会影响接收准确性。

举报

举报

举报

举报

举报

举报