目前使用的身份认证技术可以分为三种类型:基于所知、所有以及基于个人生物特征的认证。认证方式包括口令认证、智能卡认证以及指纹、虹膜等生物认证方式。

口令认证是最为广泛的一种认证方式,从普通的计算机登录系统到网络邮件系统都采用这种方式。但是,口令认证的安全性比较低,容易被他人盗用。基于指纹、虹膜的生物身份认证方式是生物技术在信息安全领域的应用,具有普遍性和唯一性的特点,但基于生物识别设备成本和识别技术水平的考虑,目前还难以得到大规模普及。基于智能卡的身份认证方式结合了硬件技术和身份认证技术的优点,提供安全可靠的认证手段,是目前迅速发展的一种认证方式。

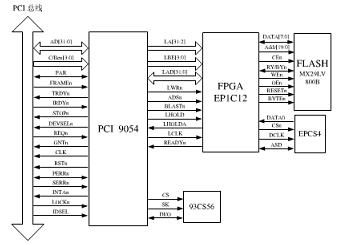

本文提出了一种基于FPGA的身份认证智能卡的设计方案。在FPGA内部实现身份认证相关的数据加密运算,加密算法采用128 bit Rijndael算法。相关的身份信息和加密运算所需要的常量数据均存放在FLASH存储器中,加密后的数据通过PCI总线传给计算机系统。

1 身份认证系统概述

身份认证是指通信双方可靠地验证对方的身份。参与身份认证的双方根据功能的不同分别被称为认证方和被认证方。被认证方向认证方发起认证请求,同时提交自己的身份信息。认证方响应认证请求,检验被认证方提交的身份信息,并将认证结果返回被认证方。在这个过程中身份信息一般是通过网络传递。由于网络开放性的特点,使得身份信息可能在传递的过程中被泄露。因此一般不直接传递被认证方的身份信息,而将身份信息加密后再传递,这样即使加密信息被攻击者截获,攻击者也无法解密信息获得被认证方的身份信息。这就要求在身份认证中所使用的密码算法具有足够高的安全强度。

Rijndael算法是美国国家标准和技术研究所(NIST)推荐的高级数据加密标准(Advanced Encryption Standard)[2],是一种分组密码算法,可以根据加密等级的不同采用128 bit、192 bit和256 bit三种不同的分组长度,具有易于软硬件实现、安全性能好、效率高和灵活等优点。

Rijndael算法中主要运算模块都是规则的逻辑运算,如置换,循环移位,多轮迭代和模2加等,适合在逻辑资源丰富的FPGA中实现[3]。以ByteSub置换为例,该模块是Rijndael算法中唯一的非线性变换部件,是决定算法安全性的关键。利用软件实现要进行大量矩阵运算,而在FPGA中可以用地址线译码直接在FPGA内部的LUT(Look Up Table)逻辑中查表完成。

基于智能卡的身份认证系统认证主要流程均在智能卡内部完成。相关的身份信息和中间运算结果均不会出现在计算机系统中。为了防止智能卡被他人盗用,智能卡一般提供使用者个人身份信息验证功能,只有输入正确的身份信息码(PIN),才能使用智能卡。这样即使智能卡被盗,由于盗用者不知道正确的身份信息码仍将无法使用智能卡。智能卡和口令技术相结合提高了基于智能卡的身份认证系统安全性。

基于智能卡的身份认证系统中采用共享密钥的身份认证协议。假设认证方和被认证方共享一个密钥K。身份认证流程如下:

(1) 被认证方向认证方发起认证请求,并提供自己的IDi。

(2) 认证方首先查找合法用户列表中是否存在IDi,如果不存在则停止下面的操作,返回被认证方一个错误信息。如果存在IDi,则认证方随机产生一个128 bit的随机数N,将N传给被认证方。

(3) 被认证方接收到128 bit的随机数N后,将N送入智能卡输入数据寄存器中,发出身份信息加密命令,智能卡利用存储在硬件中的共享密钥K采用Rijndael算法对随机数N进行加密,加密后的结果存放在输出数据寄存器中。

(4) 被认证方从智能卡输出数据寄存器中取得加密后的数据,传给认证方。认证方同样通过智能卡完成共享密钥K对随机数N的加密,如果加密结果和被认证方传来的数据一致则认可被认证方的身份,否则不认可被认证方的身份。

这个过程实现了认证方对被认证方的单向认证。在某些需要通信双方相互认证的情况下,通信双方互换角色再经过一遍同样操作流程就可完成双向认证。由于每次认证选择的随机数都不相同,因此可以防止攻击者利用截获的加密身份信息进行重放攻击。

目前使用的身份认证技术可以分为三种类型:基于所知、所有以及基于个人生物特征的认证。认证方式包括口令认证、智能卡认证以及指纹、虹膜等生物认证方式。

口令认证是最为广泛的一种认证方式,从普通的计算机登录系统到网络邮件系统都采用这种方式。但是,口令认证的安全性比较低,容易被他人盗用。基于指纹、虹膜的生物身份认证方式是生物技术在信息安全领域的应用,具有普遍性和唯一性的特点,但基于生物识别设备成本和识别技术水平的考虑,目前还难以得到大规模普及。基于智能卡的身份认证方式结合了硬件技术和身份认证技术的优点,提供安全可靠的认证手段,是目前迅速发展的一种认证方式。

本文提出了一种基于FPGA的身份认证智能卡的设计方案。在FPGA内部实现身份认证相关的数据加密运算,加密算法采用128 bit Rijndael算法。相关的身份信息和加密运算所需要的常量数据均存放在FLASH存储器中,加密后的数据通过PCI总线传给计算机系统。

1 身份认证系统概述

身份认证是指通信双方可靠地验证对方的身份。参与身份认证的双方根据功能的不同分别被称为认证方和被认证方。被认证方向认证方发起认证请求,同时提交自己的身份信息。认证方响应认证请求,检验被认证方提交的身份信息,并将认证结果返回被认证方。在这个过程中身份信息一般是通过网络传递。由于网络开放性的特点,使得身份信息可能在传递的过程中被泄露。因此一般不直接传递被认证方的身份信息,而将身份信息加密后再传递,这样即使加密信息被攻击者截获,攻击者也无法解密信息获得被认证方的身份信息。这就要求在身份认证中所使用的密码算法具有足够高的安全强度。

Rijndael算法是美国国家标准和技术研究所(NIST)推荐的高级数据加密标准(Advanced Encryption Standard)[2],是一种分组密码算法,可以根据加密等级的不同采用128 bit、192 bit和256 bit三种不同的分组长度,具有易于软硬件实现、安全性能好、效率高和灵活等优点。

Rijndael算法中主要运算模块都是规则的逻辑运算,如置换,循环移位,多轮迭代和模2加等,适合在逻辑资源丰富的FPGA中实现[3]。以ByteSub置换为例,该模块是Rijndael算法中唯一的非线性变换部件,是决定算法安全性的关键。利用软件实现要进行大量矩阵运算,而在FPGA中可以用地址线译码直接在FPGA内部的LUT(Look Up Table)逻辑中查表完成。

基于智能卡的身份认证系统认证主要流程均在智能卡内部完成。相关的身份信息和中间运算结果均不会出现在计算机系统中。为了防止智能卡被他人盗用,智能卡一般提供使用者个人身份信息验证功能,只有输入正确的身份信息码(PIN),才能使用智能卡。这样即使智能卡被盗,由于盗用者不知道正确的身份信息码仍将无法使用智能卡。智能卡和口令技术相结合提高了基于智能卡的身份认证系统安全性。

基于智能卡的身份认证系统中采用共享密钥的身份认证协议。假设认证方和被认证方共享一个密钥K。身份认证流程如下:

(1) 被认证方向认证方发起认证请求,并提供自己的IDi。

(2) 认证方首先查找合法用户列表中是否存在IDi,如果不存在则停止下面的操作,返回被认证方一个错误信息。如果存在IDi,则认证方随机产生一个128 bit的随机数N,将N传给被认证方。

(3) 被认证方接收到128 bit的随机数N后,将N送入智能卡输入数据寄存器中,发出身份信息加密命令,智能卡利用存储在硬件中的共享密钥K采用Rijndael算法对随机数N进行加密,加密后的结果存放在输出数据寄存器中。

(4) 被认证方从智能卡输出数据寄存器中取得加密后的数据,传给认证方。认证方同样通过智能卡完成共享密钥K对随机数N的加密,如果加密结果和被认证方传来的数据一致则认可被认证方的身份,否则不认可被认证方的身份。

这个过程实现了认证方对被认证方的单向认证。在某些需要通信双方相互认证的情况下,通信双方互换角色再经过一遍同样操作流程就可完成双向认证。由于每次认证选择的随机数都不相同,因此可以防止攻击者利用截获的加密身份信息进行重放攻击。

举报

举报

举报

举报

举报

举报

举报

举报