随着工艺技术的进步,存储器密度大约每 12 至 18 个月即提高一倍。对于 NAND 闪存而言,这意味着对多层单元 (MLC) 技术的重视程度日益提高。传统的单层单元 (SLC) NAND 闪存每个存储单位能够存储一个数据位。MLC 技术能够实现在单个存储单元中存放多个数据位,数据的存储容量达到相同大小 NAND 闪存设备的两倍。MLC NAND进一步加快了 NAND 闪存的每字节成本,并为新的应用提供了发展空间。市场趋势显示MLC 闪存的出货量在 2007 年初超过了 SLC 闪存。

MLC NAND 的采用,NAND 产品周期的缩短让系统设计人员的工作越来越复杂。传统的SLC NAND 闪存,每 512 字节只需要一位错误校验码,大多数新型嵌入式处理器都可以直接为其提供支持。而现在的 MLC 闪存设备却不同,需要每 512 字节扇区 4 位校验码,将来的 MLC NAND 对 ECC 的要求将超过每 512 字节扇区 8 位校验。高级 ECC 算法的实现和硬件加速电路对嵌入式处理器和主机系统在设计方面构成了很大的挑战。

系统设计人员还必须能够应对 NAND 闪存的快速更新换代,以及不同供应商之间产品功能差别带来的挑战。系统设计人员和处理器制造商为跟上 NAND 闪存制造商的步伐必须在硬件和软件开发方面进行更多资源投入。更为重要的是,额外的开发工作可能会对上市时间产生较大影响。

随着工艺技术的进步,存储器密度大约每 12 至 18 个月即提高一倍。对于 NAND 闪存而言,这意味着对多层单元 (MLC) 技术的重视程度日益提高。传统的单层单元 (SLC) NAND 闪存每个存储单位能够存储一个数据位。MLC 技术能够实现在单个存储单元中存放多个数据位,数据的存储容量达到相同大小 NAND 闪存设备的两倍。MLC NAND进一步加快了 NAND 闪存的每字节成本,并为新的应用提供了发展空间。市场趋势显示MLC 闪存的出货量在 2007 年初超过了 SLC 闪存。

MLC NAND 的采用,NAND 产品周期的缩短让系统设计人员的工作越来越复杂。传统的SLC NAND 闪存,每 512 字节只需要一位错误校验码,大多数新型嵌入式处理器都可以直接为其提供支持。而现在的 MLC 闪存设备却不同,需要每 512 字节扇区 4 位校验码,将来的 MLC NAND 对 ECC 的要求将超过每 512 字节扇区 8 位校验。高级 ECC 算法的实现和硬件加速电路对嵌入式处理器和主机系统在设计方面构成了很大的挑战。

系统设计人员还必须能够应对 NAND 闪存的快速更新换代,以及不同供应商之间产品功能差别带来的挑战。系统设计人员和处理器制造商为跟上 NAND 闪存制造商的步伐必须在硬件和软件开发方面进行更多资源投入。更为重要的是,额外的开发工作可能会对上市时间产生较大影响。

举报

举报

举报

举报

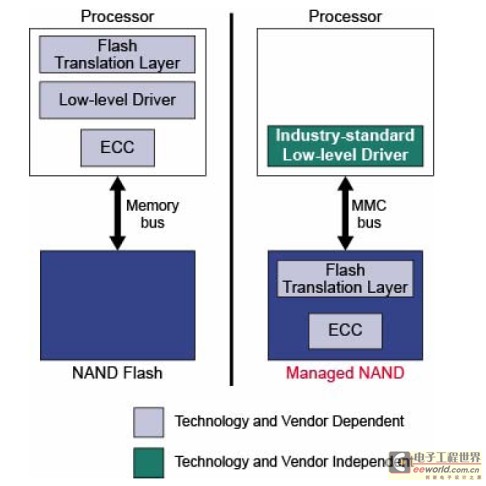

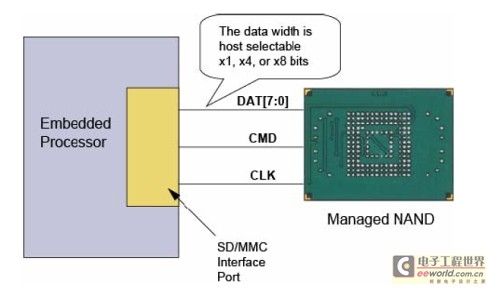

图 1:NAND 闪存配置可管理 NAND 功能

图 1:NAND 闪存配置可管理 NAND 功能 表 1:可管理 NAND 属性

表 1:可管理 NAND 属性  图 2:可管理 NAND 封装细节

图 2:可管理 NAND 封装细节

举报

举报

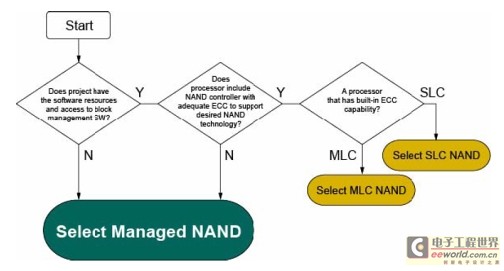

图 3:NAND 存储器选择树形图

图 3:NAND 存储器选择树形图  图 4:系统结构示意图

图 4:系统结构示意图

举报

举报

举报

举报