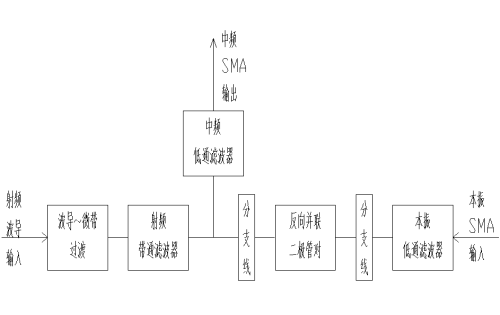

图1 谐波混频原理框图

图1 谐波混频原理框图

,L、C是单位长度的分布串联电感、分布并联电容。通过增大L、C就能减小波速v,得到慢波特性。

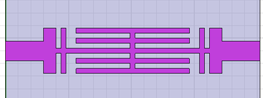

,L、C是单位长度的分布串联电感、分布并联电容。通过增大L、C就能减小波速v,得到慢波特性。 图2 CMRC低通滤波器

图2 CMRC低通滤波器 图3 CMRC滤波器等效电路

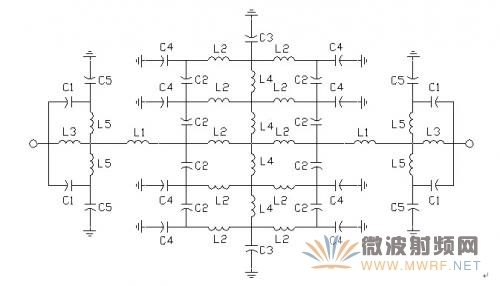

图3 CMRC滤波器等效电路

1

举报

1

举报

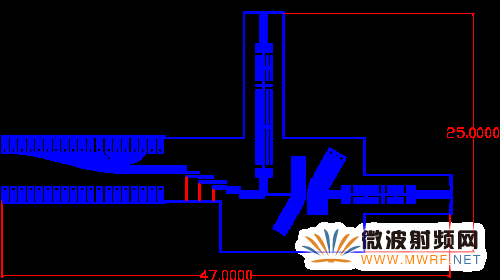

图4 波导~微带鮨线过渡

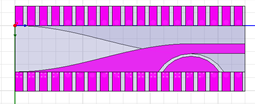

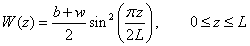

图4 波导~微带鮨线过渡 这里W(z)是渐变线宽,b是波导窄边宽度(3.556mm),w是50欧微带线宽度(0.76mm),L是渐变段总长(13mm)。图中右下方的120度金属弧块是为了降低谐振频率,确保其落在有用通带之外。上下两边的通孔条带是为了阻断纵向电流,减小通带损耗。三维电磁场仿真软件HFSS仿真结果如图5:

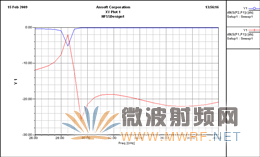

这里W(z)是渐变线宽,b是波导窄边宽度(3.556mm),w是50欧微带线宽度(0.76mm),L是渐变段总长(13mm)。图中右下方的120度金属弧块是为了降低谐振频率,确保其落在有用通带之外。上下两边的通孔条带是为了阻断纵向电流,减小通带损耗。三维电磁场仿真软件HFSS仿真结果如图5: 图5 波导-微带过渡

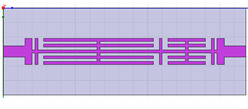

图5 波导-微带过渡 图6 两级CMRC中频端滤波器

图6 两级CMRC中频端滤波器 图7 中频端滤波器仿真结果

图7 中频端滤波器仿真结果 图8 本振端滤波器仿真结果

图8 本振端滤波器仿真结果 图9 整体电路加工图

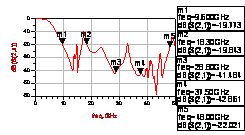

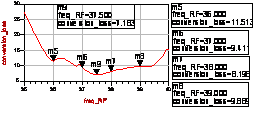

图9 整体电路加工图 图10 Ka波段四次谐波混频器变频损耗

图10 Ka波段四次谐波混频器变频损耗

举报

举报

更多回帖