先进嵌入式DC-DC转换器的要求

许多工业系统,如测试测量设备,都需要嵌入式DC-DC转换器,是因为这些应用所需的计算能力日益增加。这种计算能力由DSP 、FPGA 、数字ASIC 和微控制器 提供,而得益于工艺几何尺寸的日益缩小,该类器件在不断的进步。另一方面,这也带来了三大要求:第一,电源电压越来越低 (当然,还有容许的电压纹波和负载变化);其次,电源电流逐渐变大;第三,这些IC 通常需要为内核和I/O结构以准确的顺序提供单独的电压,以避免闩锁现象的发生。

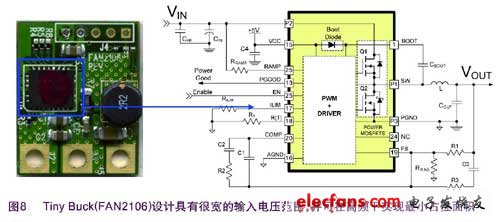

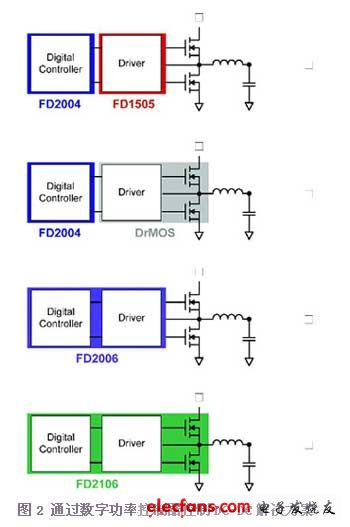

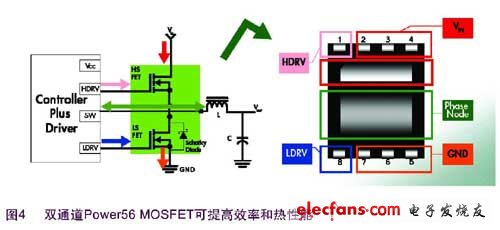

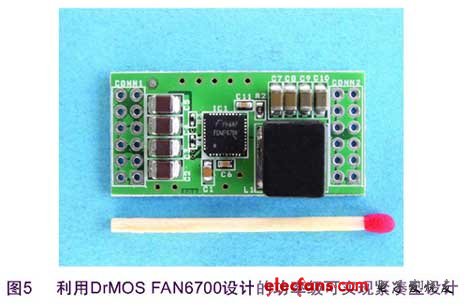

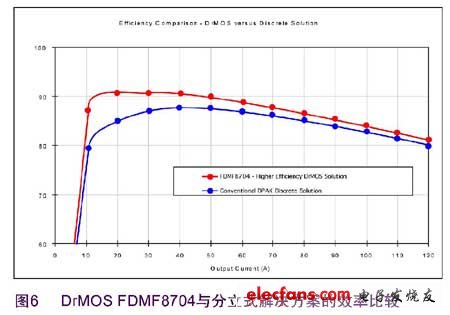

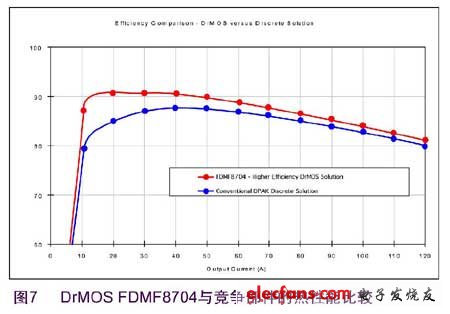

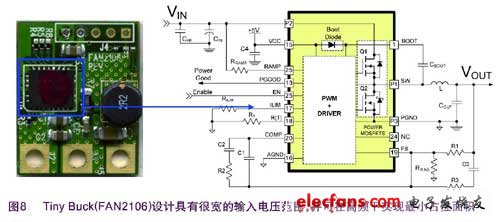

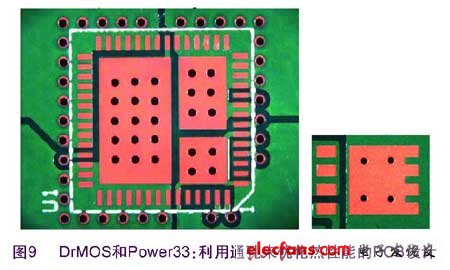

嵌入式DC-DC转换器必须具有出色的效率。这类转换器的可用空间很小,对于热设计尤其具有挑战性,因为嵌入式转换器主要依赖PCB 上元件周围的铜面积来改善系统热阻抗。由于功耗与电流的平方成正比,随着负载电流的增加,这种情形会更加恶化。因此这时需要低导通阻抗RDSON、低开关损耗的电源开关。不过鉴于器件的导通阻抗RDSON越低,寄生电容 乃至开关损耗就越高,最终功耗也越高,故必需进行一定的权衡取舍。嵌入式DC-DC转换器的另一个主要要求是EMI必需低。这些转换器产生的噪声会对周围的电路造成干扰,因而必须尽可能地小。不过,高速 (以降低开关损耗) 转换大电流 (若负载所需) 不可避免地会产生很大的开关噪声,包括传导噪声和辐射噪声 (主要是磁场)。因此,必需特别关注功率级元件选择和布局的优化,尤其是在驱动器连接方面。此外,PWM控制拓扑也有一定影响。

举例来说,采用0.09μm技术的数字IC可能需要1.2V ± 40mV的电源电压。根据该DSP的数据表,其电源电流可高达952mA。另一个例子是65nm工艺制造的大尺寸FPGA,1.0V +/-50mV电源电压、85℃时,需要4.2 A的闲置电源电流。在工作模式下,按照具体配置情况,电流可增至18A,因在高开关频率下,动态要求非常高。

这些应用中包含多个不同IC相当常见,譬如,由一个较小的微控制器 (电源电压较高时) 来负责所有的接口和主机功能,利用一个较大的DSP或专用硬件来执行计算密集型功能。很多时候,还专门使用另有一套电压要求的高性能A/D转换器来改善噪声性能,真正充分利用这些转换器的分辨率和带宽。这些趋势催生出具有众多相倚关系的复杂的功率管理系统。

先进嵌入式DC-DC转换器的要求

许多工业系统,如测试测量设备,都需要嵌入式DC-DC转换器,是因为这些应用所需的计算能力日益增加。这种计算能力由DSP 、FPGA 、数字ASIC 和微控制器 提供,而得益于工艺几何尺寸的日益缩小,该类器件在不断的进步。另一方面,这也带来了三大要求:第一,电源电压越来越低 (当然,还有容许的电压纹波和负载变化);其次,电源电流逐渐变大;第三,这些IC 通常需要为内核和I/O结构以准确的顺序提供单独的电压,以避免闩锁现象的发生。

嵌入式DC-DC转换器必须具有出色的效率。这类转换器的可用空间很小,对于热设计尤其具有挑战性,因为嵌入式转换器主要依赖PCB 上元件周围的铜面积来改善系统热阻抗。由于功耗与电流的平方成正比,随着负载电流的增加,这种情形会更加恶化。因此这时需要低导通阻抗RDSON、低开关损耗的电源开关。不过鉴于器件的导通阻抗RDSON越低,寄生电容 乃至开关损耗就越高,最终功耗也越高,故必需进行一定的权衡取舍。嵌入式DC-DC转换器的另一个主要要求是EMI必需低。这些转换器产生的噪声会对周围的电路造成干扰,因而必须尽可能地小。不过,高速 (以降低开关损耗) 转换大电流 (若负载所需) 不可避免地会产生很大的开关噪声,包括传导噪声和辐射噪声 (主要是磁场)。因此,必需特别关注功率级元件选择和布局的优化,尤其是在驱动器连接方面。此外,PWM控制拓扑也有一定影响。

举例来说,采用0.09μm技术的数字IC可能需要1.2V ± 40mV的电源电压。根据该DSP的数据表,其电源电流可高达952mA。另一个例子是65nm工艺制造的大尺寸FPGA,1.0V +/-50mV电源电压、85℃时,需要4.2 A的闲置电源电流。在工作模式下,按照具体配置情况,电流可增至18A,因在高开关频率下,动态要求非常高。

这些应用中包含多个不同IC相当常见,譬如,由一个较小的微控制器 (电源电压较高时) 来负责所有的接口和主机功能,利用一个较大的DSP或专用硬件来执行计算密集型功能。很多时候,还专门使用另有一套电压要求的高性能A/D转换器来改善噪声性能,真正充分利用这些转换器的分辨率和带宽。这些趋势催生出具有众多相倚关系的复杂的功率管理系统。

举报

举报

举报

举报

举报

举报

举报

举报