3 功能编译、设计仿真与硬件下载

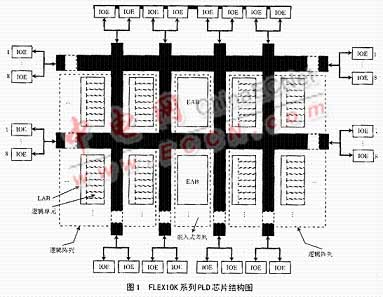

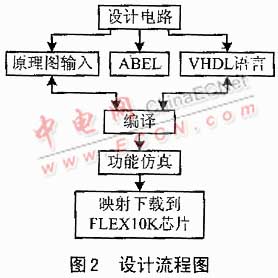

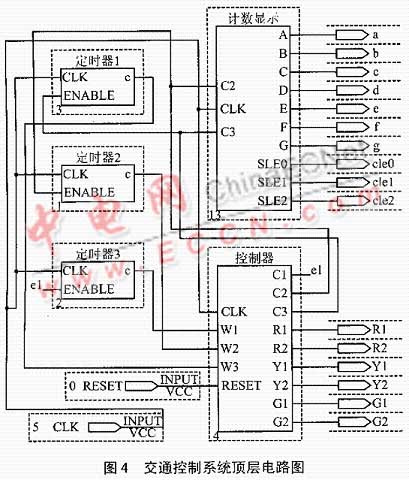

本系统采用Altera公司生产的FLEX10K系列的CPLD芯片,应用该公司的MAX+PLUS II开发软件完成设计后,需对各种源文件从低层到顶层逐个编译,再进行逻辑仿真。选择器件后,打开检查项目中所有设计文件,通过检测发发现在编程器件中可能存在的可靠性不好的逻辑器件引脚分配。

Altera公司推荐的编译器可自动为项目进行引脚分配,也可人工调整引脚。在编译器窗口选择Start按钮,将对所有设计的项目进行处理,出现错误将给出具体错误提示。为了保证设计的正确性,在编译通过后,还需进行逻辑仿真。仿真通过后再应用MAX+PLUS II的编程器对所选可编程逻辑器件下载编程,便完成了交通控制系统的ASIC芯片设计和硬件固化。若在芯片外围接入必要电源、脉冲信号、显示器和指示灯,便构成了一个完整交通控制系统。它具有工作稳定、体积小、在线修改方便等特点。

3 功能编译、设计仿真与硬件下载

本系统采用Altera公司生产的FLEX10K系列的CPLD芯片,应用该公司的MAX+PLUS II开发软件完成设计后,需对各种源文件从低层到顶层逐个编译,再进行逻辑仿真。选择器件后,打开检查项目中所有设计文件,通过检测发发现在编程器件中可能存在的可靠性不好的逻辑器件引脚分配。

Altera公司推荐的编译器可自动为项目进行引脚分配,也可人工调整引脚。在编译器窗口选择Start按钮,将对所有设计的项目进行处理,出现错误将给出具体错误提示。为了保证设计的正确性,在编译通过后,还需进行逻辑仿真。仿真通过后再应用MAX+PLUS II的编程器对所选可编程逻辑器件下载编程,便完成了交通控制系统的ASIC芯片设计和硬件固化。若在芯片外围接入必要电源、脉冲信号、显示器和指示灯,便构成了一个完整交通控制系统。它具有工作稳定、体积小、在线修改方便等特点。

举报

举报

举报

举报

举报

举报