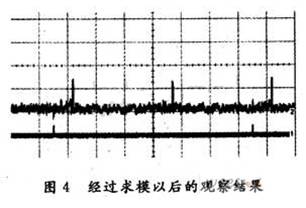

由于雷达所处的环境的复杂性,除了地物、云雨、鸟群等干扰外,还可能来自临近的雷达异步干扰、电台干扰等。所有的干扰,经过接收机进入信号处理机,虽然经过了中频信号的处理,但还可能有残余。因此,为了得到更好的检测性能,在检测前进行一次视频积累是非常必要的。

虽然视频积累的效果不如相参积累,但是视频积累的工程实现比较简单,对雷达的收发系统没有严格的相参性要求,且对大多数运动目标来讲其回波的起伏将明显破坏相邻回波信号的相位相参性,因此在许多实际工程应用场合还是采用视频积累。

举报

举报

举报

举报

更多回帖