什么是分布式干扰系统?分布式干扰系统 是一种综合化、一体化、小型化、网络化和智能化系统,是将众多体积小,重量轻,廉价的小功率侦察干扰机装置在易于投放的小型平台上,撒布在接近***扰目标空域地,通过指令启动,自主组网,并根据控制对敌方雷达网、

通信网、制导网和预警机等

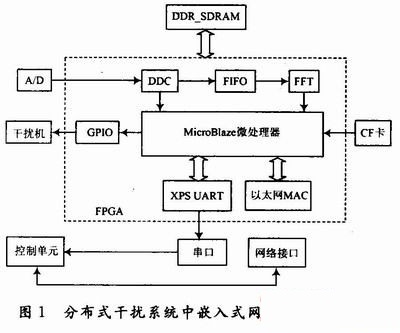

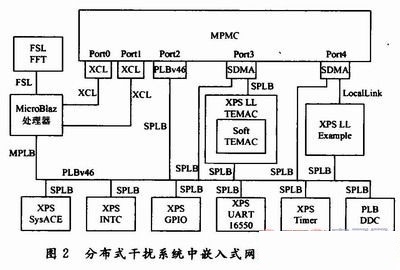

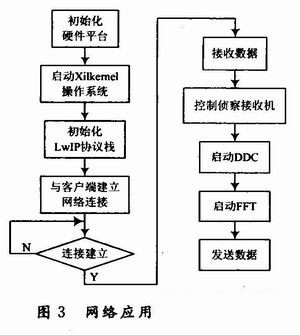

电子信息系统实施接近式侦察和干扰,这将在未来的电子对抗中发挥重要作用。分布式干扰系统采用逼近的分布式网络化结构,形成一种“面对面”的电子战系统,共同完成对敌信号的探测、定位、干扰任务。因此,嵌入式网关是分布式干扰系统研究的关键技术之一。目前国内对分布式干扰系统的研究还停留在理论基础上,而对其关键技术的研究不多。怎么利用嵌入式网关设计分布式干扰系统?这个问题急需解决。

举报

举报

举报

举报