嵌入式设备由于具有硬件可在线配置,实现灵活等特点,使得其应用越来越广泛。尤其在基于FPGA的硬件系统中应用较多,目前在许多产品中实现了嵌入式网口、嵌入式PCI/PCI-E、嵌入式USB等各种模块。但在DSP中实现嵌入式设备还比较少,一般DSP都直接集成这些设备模块,用户选择不同型号的DSP芯片以满足产品应用要求。但对于一些较为特殊的嵌入式设备,DSP也可以实现该功能。

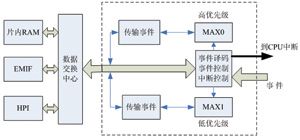

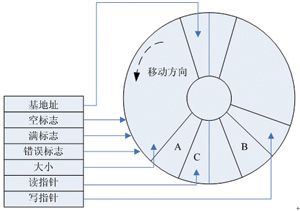

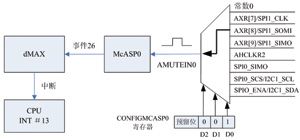

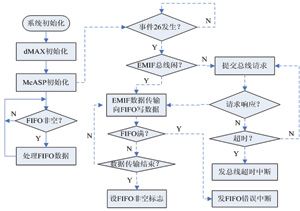

ti公司的DSP芯片C6727B,由于其片内集成dMAX模块,使得实现嵌入式FIFO成为可能。其实现嵌入式FIFO的本质就是将DSP的片内一段RAM空间设置成FIFO空间,FIFO和外部设备的数据交换由EMIF接口完成。该FIFO的数据读写不需要DSP的CPU参与,从而提高整个系统性能,实现数据交换和数据处理的同时进行。如何设计嵌入式FIFO数据传输系统?该怎么进行设计、配置及其使用?这些问题谁知道答案吗?

举报

举报

举报

举报

更多回帖