无论从微观到宏观、从延长电池寿命到减少全球变暖的温室效应等等,各种不同因素都在迅速推动系统设计人员关注节能问题。一项有关设计优先考虑事项的最新调查指出,大部分工程师已把功耗排在首位,或者是将其紧跟在性能、密度和成本之后。

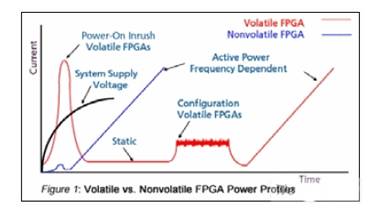

在功耗方面,FPGA带来了独特的挑战。为什么要设计优化FPGA功耗?

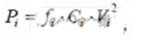

这里fi为开关频率, Ci为电容性负载,Vi为该资源的电压摆幅。充分考虑动态功率方程中的每一项,便可以降低功耗。例如,在时钟域可以决定设计的哪些部分需要快速时钟或较慢时钟。开关频率fi是动态功率方程的成分之一。由快速时钟驱动的逻辑相比由慢速时钟驱动的逻辑,开关更频繁。设计人员知道逻辑的哪些部分需要快速时钟,而哪些部分又可以运行在较慢速度之下,因此可以按照时钟所控制的功能予以划分,从而节省功率。

这里fi为开关频率, Ci为电容性负载,Vi为该资源的电压摆幅。充分考虑动态功率方程中的每一项,便可以降低功耗。例如,在时钟域可以决定设计的哪些部分需要快速时钟或较慢时钟。开关频率fi是动态功率方程的成分之一。由快速时钟驱动的逻辑相比由慢速时钟驱动的逻辑,开关更频繁。设计人员知道逻辑的哪些部分需要快速时钟,而哪些部分又可以运行在较慢速度之下,因此可以按照时钟所控制的功能予以划分,从而节省功率。

举报

举报

举报

举报

更多回帖