SDH设备时钟(SEC)是SDH光传输系统的重要组成部分,是SDH设备构建同步网的基础,也是同步数字体系(SDH)可靠工作的前提。SEC的核心部件由锁相环构成。网元通过锁相环跟踪同步定时基准,并通过锁相环的滤波特性对基准时钟在传输过程中产生的抖动和漂移进行过滤。而当基准源不可用时,则由SEC提供本地的定时基准信息,实现高质量的时钟输出。

SEC需要满足ITU-T G.813建议[1]中的相关指标要求。SEC可以工作在自由振荡、跟踪、保持三种模式下,并且能够在三种模式之间进行平滑切换。由于ITU-T G.813建议规定的SEC带宽较窄(-3db带宽在1~10Hz内),且需要在三种工作模式下输出稳定的时钟,同时还要保证在三种模式切换过程中输出时钟稳定(即平滑切换),采用模拟锁相环(APLL)很难实现。因此一般采用数字锁相环(DPLL)实现SEC[2];也有许多芯片厂商直接采用单片集成

电路芯片实现SEC,如SEMTECH公司的ACS8520[3]等。

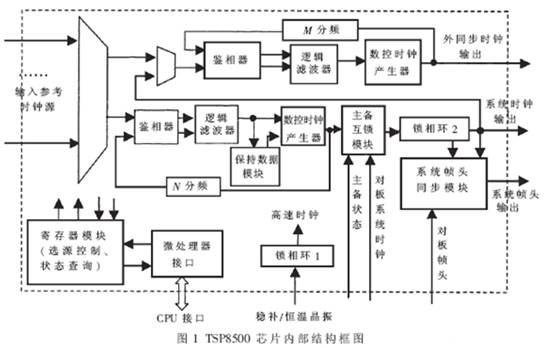

本文介绍一种采用单片现场可编程门阵列(

FPGA)芯片实现SEC功能的方案,在此将用FPGA设计的SEC功能芯片命名为TSP8500。

举报

举报

function ImgZoom(Id)//重新设置图片大小 防止撑破表格 { var w = $(Id).width; var m = 650; if(w

function ImgZoom(Id)//重新设置图片大小 防止撑破表格 { var w = $(Id).width; var m = 650; if(w

举报

举报