本文小结

串行RapidIO正在越来越多的新应用中崭露头角,特别是在采用DSP的有线和无线应用中在Xilinx器件中实现串行RapidIO主要有以下优势:

1. Xilinx提供了完整的SRIO端点方案;

2. 可利用同样的软、硬件结构,通过灵活的调整,实现不同类型的产品;

3. 由于Xilinx器件采用了新型GTP收发机和65nm 技术,因此功耗很低;

4. 通过CoreGen GUI 可实现方便的可配置性和灵活性;

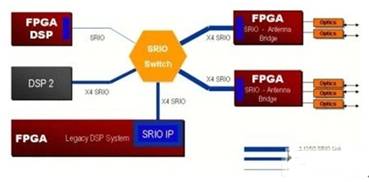

5. 由于业界领先的厂商都有器件支持SRIO连接,因而硬件互通性有保证;

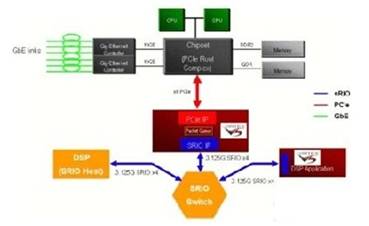

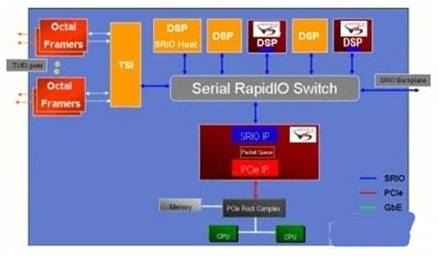

6. 可通过使用PCIe和TEMAC等集成IO模块实现系统集成,从而降低系统整体成本。

本文小结

串行RapidIO正在越来越多的新应用中崭露头角,特别是在采用DSP的有线和无线应用中在Xilinx器件中实现串行RapidIO主要有以下优势:

1. Xilinx提供了完整的SRIO端点方案;

2. 可利用同样的软、硬件结构,通过灵活的调整,实现不同类型的产品;

3. 由于Xilinx器件采用了新型GTP收发机和65nm 技术,因此功耗很低;

4. 通过CoreGen GUI 可实现方便的可配置性和灵活性;

5. 由于业界领先的厂商都有器件支持SRIO连接,因而硬件互通性有保证;

6. 可通过使用PCIe和TEMAC等集成IO模块实现系统集成,从而降低系统整体成本。

举报

举报

举报

举报

举报

举报

举报

举报