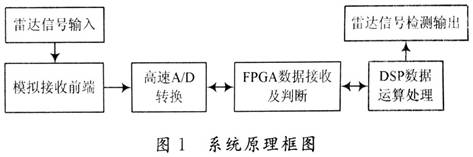

我国目前的海事雷达大多为进口雷达,有效探测距离小,在信噪比降为3 dB时已经无法识别信号。随着微

电子技术的迅猛发展,高速A/D(模拟/数字转换)和高速数字信号处理器件(Digital Signal Proeessors,DSP)、高速现场可编程逻辑器件(Field ProgrammableGate Array,

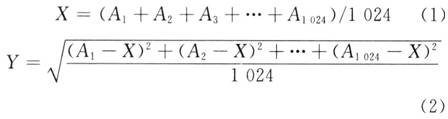

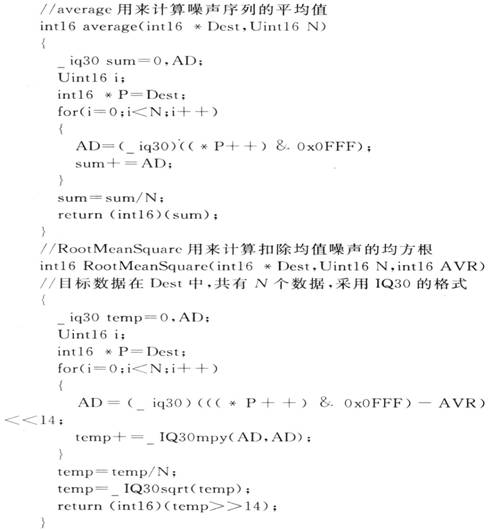

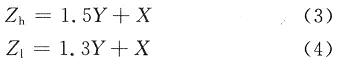

FPGA)的出现,可以在不增加现有雷达发射功率和接收灵敏度的前提下,在信噪比降为3 dB时能测到雷达信号,使雷达的有效作用距离提高。有哪些方法能检测低信噪比雷达信号 ? 可以利用DSP和FPGA技术吗?

举报

举报

举报

举报

举报

举报