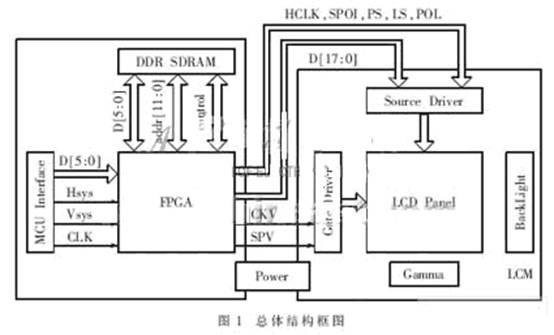

嵌入式系统可以用各种微处理器代替通用计算机的CPU,实现既定功能并驱动显示系统以方便人机交流。早期的单片机由于低时钟频率(小于5 MHz)和低I/O口数量的限制,一般只驱动像素比较少(5 000像素以内)的液晶显示器[1-2]。近年来随着制作工艺的发展和设计结构的优化[3],单片机的最高时钟频率和I/O口的数量都得到了很大提高,低耗能低电压单片机不断出现[4],新调试技术使开发过程效率更高[5],驱动几千像素的液晶显示器早已出现。然而,更友好的人机界面需要更高分辨率的液晶显示器。考察目前流行的液晶显示器驱动方式可以看到,无论使用何种单片机或作为嵌入式系统的微处理器,都会被液晶显示器的驱动控制部分占据大量资源,那么如何设计嵌入式系统的显卡方案?解决这个难题就很重要了。

举报

举报

举报

举报

举报

举报

更多回帖