0 引言

可重构体系结构已经成为FPGA系统开发的研究热点,并已有许多令人瞩目的研究成果及产品应用。FPGA可重构的应用为用户提供了方便的系统升级模式,同时也实现了基于相同硬件系统的不同工作模式功能。在当今快速发展的市场环境条件下,产品是否便于现场升级,是否便于灵活使用无疑是产品能否进入市场的关键因素,FPGA的可重构设计显得尤为重要。

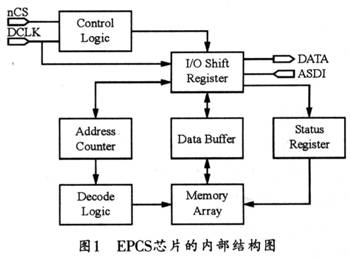

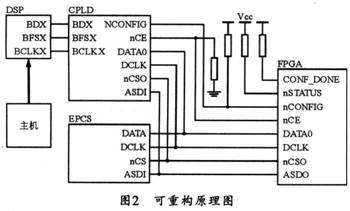

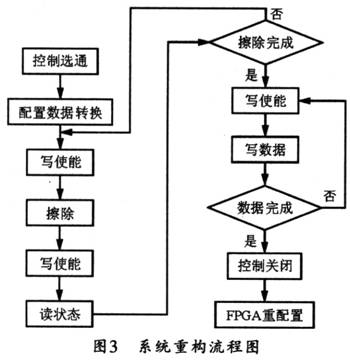

目前,很多可重构的设计方式都采用单片机、CPLD等器件直接对FPGA器件进行编程配置,从而实现系统工作模式的可重构。本设计则通过开发CPLD先对FPGA的配置芯片EPCS进行编程配置,然后再由FPGA从EPCS配置芯片下载配置程序来实现可重构,并通过用户界面的简单操作来完成FPGA的工作方式重构,这种可重构方式结构简单,配置灵活,用户操作更加方便。本文首先介绍了FPGA常用的配置方式,然后详细阐述了有什么FPGA可重构方法可以对EPCS在线编程?

举报

举报

举报

举报

更多回帖