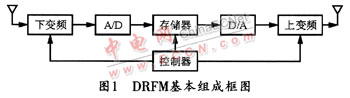

纵观世界历史,每一次新军事变革都会催生一批新技术的诞生,DRFM也不例外,它是现代

电子战中雷达对抗的产物,是一种对射频信号采样、存储、运算后转发的电子部件。当DRFM对样本信息保存下来后,可根据需要加入调制信息;再通过高速DAC转发出去,从而实现对目标的有效干扰。随着大规模集成

电路与微波集成电路的高速发展,数据采集和波形产生的工作带宽已越来越宽,信号处理的速度也越来越快,这些都使得DRFM的成本大幅降低,而处理能力大大提高,因而也得到了更为广泛的应用。DRFM作为转发式干扰的关键部件,在雷达的目标信号模拟、杂波信号模拟、无源干扰信号模拟等方面有着特殊的军事意义。

举报

举报

举报

举报

举报

举报