作者:李慧敏

0 引 言

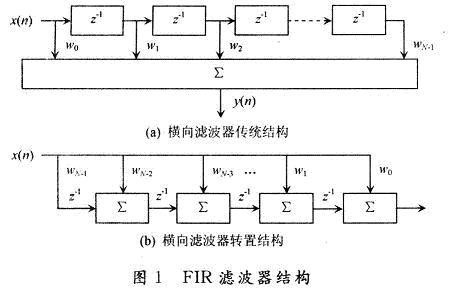

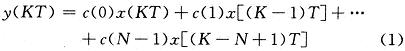

在数字信号处理领域,滤波器无疑是个非常重要的环节。而在数字滤波器中,有限脉冲响应(FIR)滤波器因为其线性相位的特点,应用尤为广泛。实际应用中FIR滤波器分为常系数FIR滤波器和变系数FIR滤波器。常系数FIR滤波器的系数固定不变,可根据其特点采用分布式算法进行设计,故实现起来速度快,消耗的资源少。变系数FIR滤波器的系数是不断变化的。当前含有变系数FIR滤波环节的芯片普遍存在速度与处理级数的矛盾,有效解决此问题具有重要的现实意义。

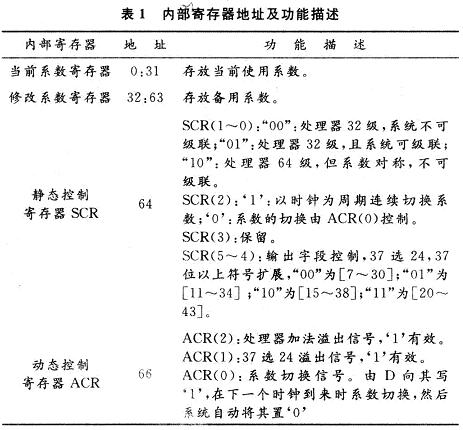

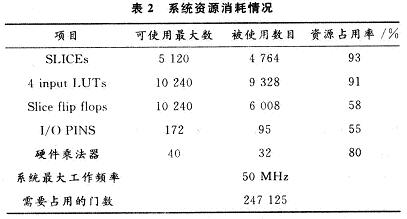

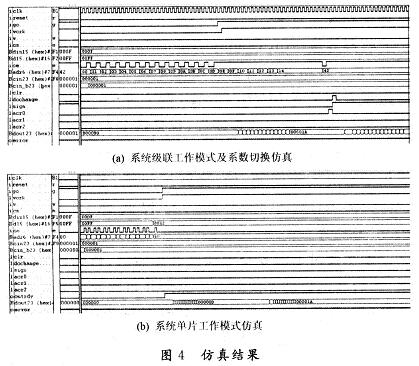

随着片上系统(SOC)时代的到来,可编程逻辑器件不仅为FIR滤波器的设计提供了一条可行而高效的方法,而且更被广泛地使用于数字信号处理的各个领域。采用INMOS公司的IMS A100级联型信号处理器为模板,以FIR滤波器设计为核心,用FPGA技术开发设计级联型信号处理器,能够应用于数字FIR滤波、高速自适应滤波、相关和卷积、离散傅里叶变换、脉冲压缩、线性预测编码语音处理、高速定点矩阵乘法等,有较好的应用前景和发展空间。

那有谁知道该如何利用FPGA实现级联信号处理器吗?

举报

举报

举报

举报

举报

举报

更多回帖