作者:*** 珠海欧比特控制工程股份有限公司

作者:*** 珠海欧比特控制工程股份有限公司

举报

举报

举报

举报

举报

举报

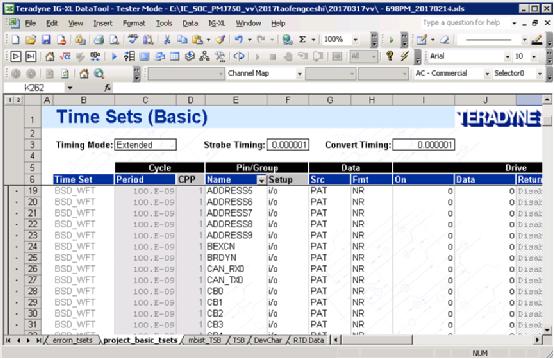

第三步骤,利用J750的测试程序导入功能,将上述两个文件导入到程序里,完成测试机的TimingSet参数等参数设定, 并根据测试机特性及S698PM时序要求可以微调参数,如下图2所示:

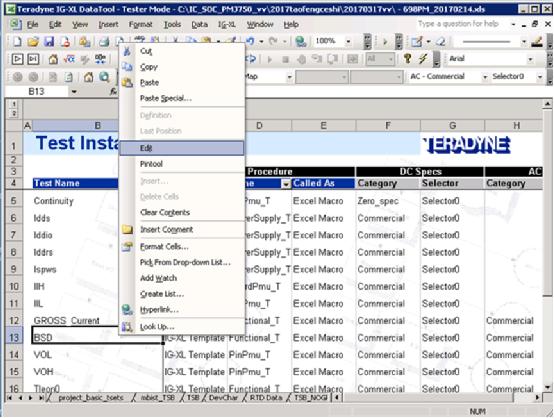

第三步骤,利用J750的测试程序导入功能,将上述两个文件导入到程序里,完成测试机的TimingSet参数等参数设定, 并根据测试机特性及S698PM时序要求可以微调参数,如下图2所示: 第四步骤,设定BSD Function Test功能模块参数,调用BSD测试程序所需的直流和交流参数,以及PATTERN文件。如下图3所示:

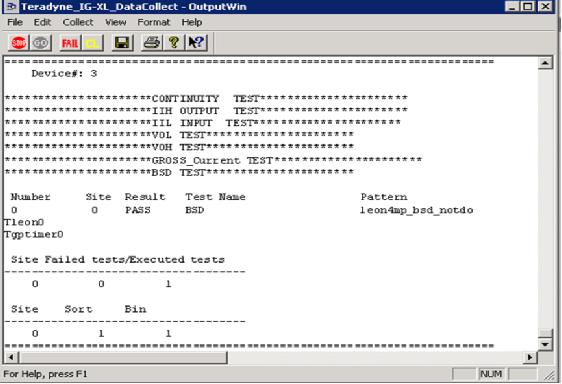

第四步骤,设定BSD Function Test功能模块参数,调用BSD测试程序所需的直流和交流参数,以及PATTERN文件。如下图3所示: 第五步骤,执行BSD function Test命令,在测试过程中,如果结果不满足要求,可进行TimingSet表格中的时间参数微调,测试结果报告如下图4所示:

第五步骤,执行BSD function Test命令,在测试过程中,如果结果不满足要求,可进行TimingSet表格中的时间参数微调,测试结果报告如下图4所示:

举报

举报

更多回帖