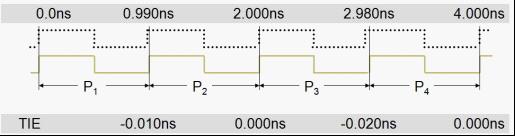

由于不断追求更高的性能,有效数据窗的单位间隔(UI)继续缩短。速率为1Gb/s时,UI为1000 ps,5Gb/s缩短为200 ps,10Gb/s则为100 ps。对于100 ps的有效数据窗,当系统没有连贯而可靠地发送和接收数据之前,可容忍很小的Tj(总抖动)。以上述速度传输时,Tj结果需大大小于100ps,而Rj(随机性抖动)只在1ps的子区间内。有什么技术和工具能用来检定这些飞秒(fs)系统呢?

基本上来说,随着速度的提高,高速I/O设计比以往面临更大挑战。最新的标准多数要求在物理层的比特误码率为10–12。然而,UI的逐渐缩小使保持这样的误码率变得越来越难。到头来,这就意味着设备级抖动要继续缩短。例如,5Gb/s的SuperSpeed USB规定Rj为2.42ps RMS;10 Gb/s的SFP规定Tj为28 ps,Rj为1 ps左右。

举报

举报

举报

举报