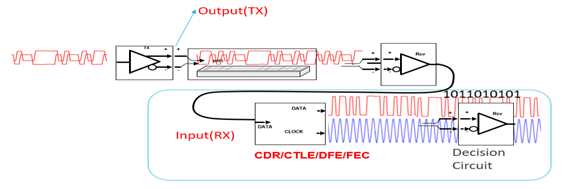

在用户进行系统或者芯片测试的时候,一般主要验证几个方面的性能和可靠性,包括系统发送端的信号质量,链路的损耗/串扰,接收端的容限。如下图1,一个链路系统的基本架构。通常在发送端会使用FFE来补偿链路的损耗,接收端会采用DFE/FFE等方法来进行均衡,一些比较高速率的标准如PCIE 4.0/5.0,SAS4等还会采用FEC来进行纠错,当然接收端还需要CDR来从串行信号里面进行时钟恢复得到同步时钟来对信号进行采样。

在用户进行系统或者芯片测试的时候,一般主要验证几个方面的性能和可靠性,包括系统发送端的信号质量,链路的损耗/串扰,接收端的容限。如下图1,一个链路系统的基本架构。通常在发送端会使用FFE来补偿链路的损耗,接收端会采用DFE/FFE等方法来进行均衡,一些比较高速率的标准如PCIE 4.0/5.0,SAS4等还会采用FEC来进行纠错,当然接收端还需要CDR来从串行信号里面进行时钟恢复得到同步时钟来对信号进行采样。

图3:BSX系列误码仪支持单通道的高速协议数据的发送和接收解析

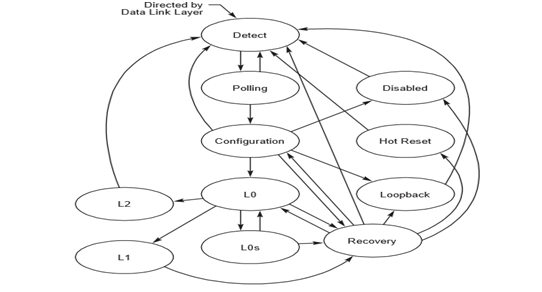

图3:BSX系列误码仪支持单通道的高速协议数据的发送和接收解析 如图3,除了loopback training以外,另一个重要的步骤是link training(链路协商),需要Bert和DUT进行FFE/DFE的实时协商来补偿链路的损耗,以达到最低的误码率。在USB3.1/PCIe协议中发送端会有多个级别的FFE来灵活对信号发送端进行均衡补偿,在接收端也会有CTLE和DFE多级组合来进行补偿。(详细的链路协商步骤细节可以参考泰克的相关应用文章-《克服第4代I/O应用中的接收机测试挑战》)。这个链路协商同样需要Bert能够在一定程度上去模拟一个真实设备和被测设备进行沟通,解析并响应被测设备的要求去调节信号输出的FFE参数,并根据误码率来请求被测设备调节其输出的FFE参数和接收端的CTLE/DFE参数,以达到最佳的误码率。同样这个时候也需要BERT具备单通道直接输出和接收并解析基于协议的码型序列达到与被测设备的实时协商。

如图3,除了loopback training以外,另一个重要的步骤是link training(链路协商),需要Bert和DUT进行FFE/DFE的实时协商来补偿链路的损耗,以达到最低的误码率。在USB3.1/PCIe协议中发送端会有多个级别的FFE来灵活对信号发送端进行均衡补偿,在接收端也会有CTLE和DFE多级组合来进行补偿。(详细的链路协商步骤细节可以参考泰克的相关应用文章-《克服第4代I/O应用中的接收机测试挑战》)。这个链路协商同样需要Bert能够在一定程度上去模拟一个真实设备和被测设备进行沟通,解析并响应被测设备的要求去调节信号输出的FFE参数,并根据误码率来请求被测设备调节其输出的FFE参数和接收端的CTLE/DFE参数,以达到最佳的误码率。同样这个时候也需要BERT具备单通道直接输出和接收并解析基于协议的码型序列达到与被测设备的实时协商。

举报

举报

举报

举报

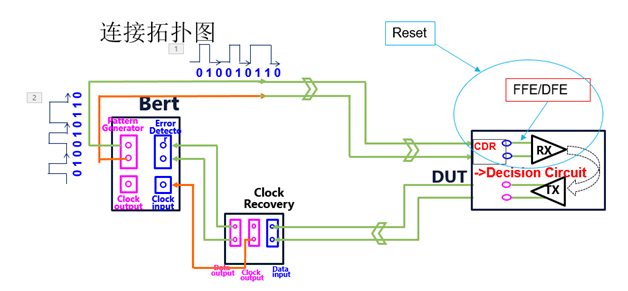

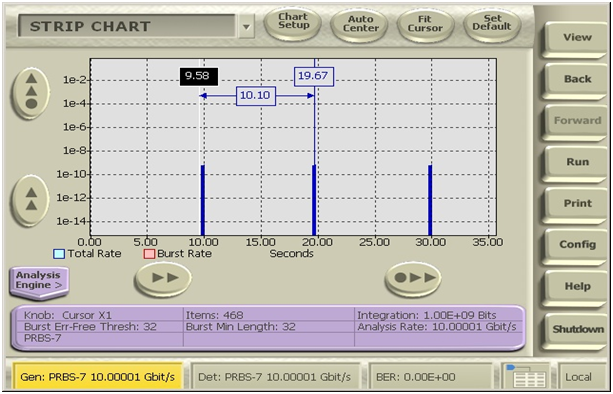

先按照上面图4的连接图连接好,将被测芯片设置为环回模式,设置Bertscope的PG输出为被测速率,码型设置为PRBS31,确认CDR模块可以正确锁定,Error Detector能够正确的Sync码型,并且测试没有误码。将Bert 的Error Detector端设置为Auto-resync。

先按照上面图4的连接图连接好,将被测芯片设置为环回模式,设置Bertscope的PG输出为被测速率,码型设置为PRBS31,确认CDR模块可以正确锁定,Error Detector能够正确的Sync码型,并且测试没有误码。将Bert 的Error Detector端设置为Auto-resync。

举报

举报

举报

举报

更多回帖