当今数据中心用的PCI Express最强大的一个功能是I/O虚拟化。I/O虚拟化让虚拟机直接访问I/O硬件设备,提高了企业级服务器的性能。单根I/O虚拟化(SR-IOV)技术规范拉动了市场。SR-IOV技术规范让一台PCI Express设备能在主机里呈现为多台不同的“虚拟”设备。这是通过在传统PCI Express功能(即实体功能)上添加一个新的PCI Express功能结构实现的。实体功能控制新型虚拟化功能的创建和分配。

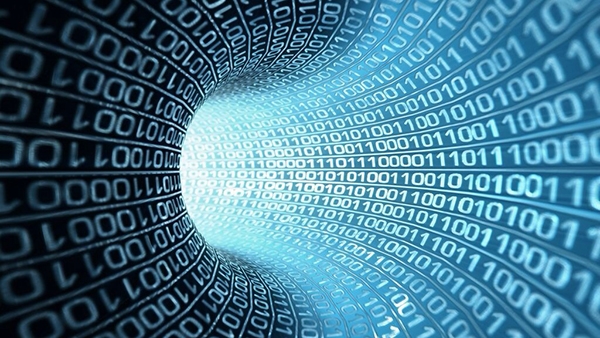

当今数据中心用的PCI Express最强大的一个功能是I/O虚拟化。I/O虚拟化让虚拟机直接访问I/O硬件设备,提高了企业级服务器的性能。单根I/O虚拟化(SR-IOV)技术规范拉动了市场。SR-IOV技术规范让一台PCI Express设备能在主机里呈现为多台不同的“虚拟”设备。这是通过在传统PCI Express功能(即实体功能)上添加一个新的PCI Express功能结构实现的。实体功能控制新型虚拟化功能的创建和分配。 图1:仍用一个PCIe接口移动数据时,虚拟化功能呈现实体功能底层硬件相互独立的视图和配置。

图1:仍用一个PCIe接口移动数据时,虚拟化功能呈现实体功能底层硬件相互独立的视图和配置。

举报

举报

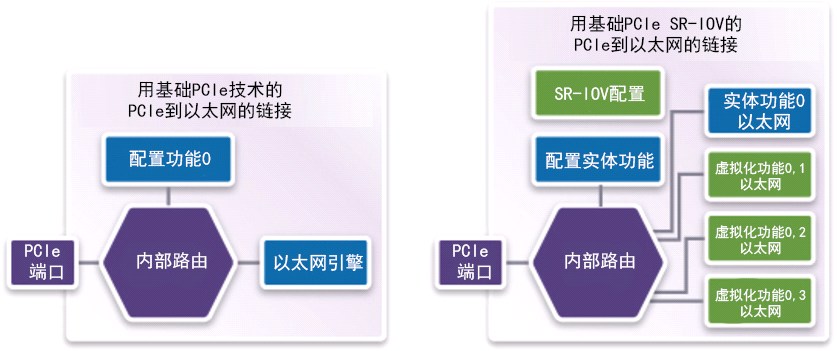

图2:因为对虚拟化功能内存区域连续定位,所以大大简化了虚拟化功能的内存地址译码。

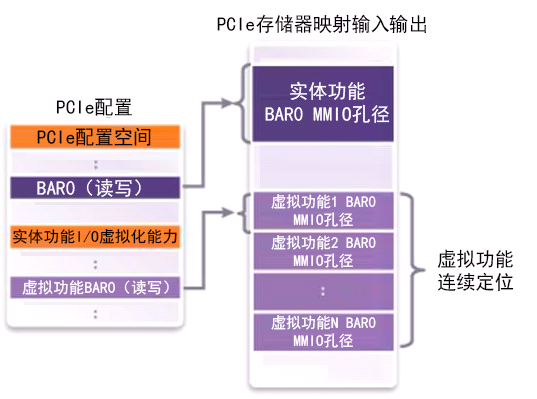

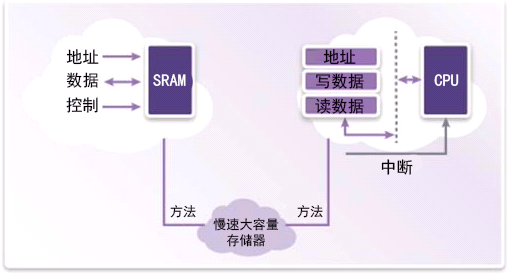

图2:因为对虚拟化功能内存区域连续定位,所以大大简化了虚拟化功能的内存地址译码。 图3:较慢的大容量存储器数据与底层实体功能信息合并,启用PCI Express控制器外部虚拟化功能配置空间的存储器。

图3:较慢的大容量存储器数据与底层实体功能信息合并,启用PCI Express控制器外部虚拟化功能配置空间的存储器。

举报

举报

图4:大容量传感器可以直接安装在片上存储器里,或者间接通过本地CPU提供读写请求。

图4:大容量传感器可以直接安装在片上存储器里,或者间接通过本地CPU提供读写请求。

举报

举报

更多回帖