随着数字技术的不断突飞猛进,越来越多的

电路系统将A/D转换器作为一个子模块集成到系统内部。例如在便携式数据传输、数字视频和图像处理等应用系统中,8~12位分辨率的嵌入式A/D转换器就是这些系统的一个非常重要的组成部分。在这些应用中,如何在保持高采样频率下降低功耗是一个很重要的设计要点。整体而言,流水线型结构A/D转换器是同时实现低功耗、高采样率和高分辨率的合理选择。

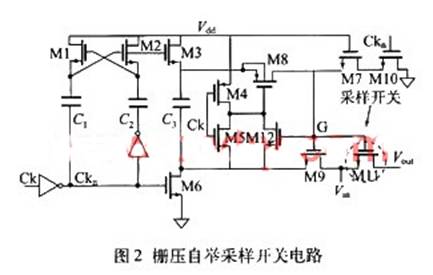

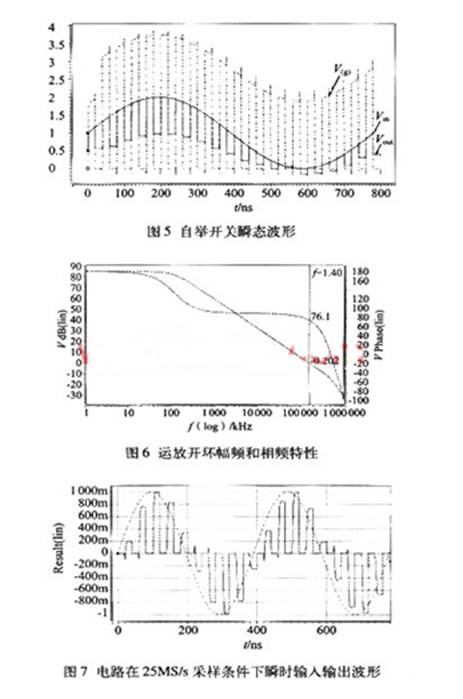

在流水线结构的A/D转换电路中,采样保持电路是整个电路的核心模块。同时采样保持电路通常是整个电路中功耗最大的模块,其性能直接决定了整个A/D转换器的性能。本文介绍了运用于视频处理系统的一种12位25MS/s低功耗采样保持电路。

举报

举报

举报

举报

举报

举报

举报

举报