大家好,

我尝试使用我的视频定时/模式发生器来操作VDMA而没有运气。

所以我建立了一个环回

v_vid_in_axi4s

v_axi4s_vid_out

所以我的IP生成

timing + DataPattern >> v_vid_in_axi4s >> AXI4-Stream >> v_axi4s_vid_out

\ ====== VTG(计时)==== //`

我配置v_axi4s_vid_out(简短:vout)参数VBG_MASTER_SLAVE = 1(主)

vout的初始化标志总是向上,没有达到锁定状态!

但是有一些我无法解决的异常情况,我希望Xilinx Video IP团队的人能够提供帮助。

Stream.TUSer每两帧错过一次

视频帧数据变得交替:一个得到正确,下一个得不到。

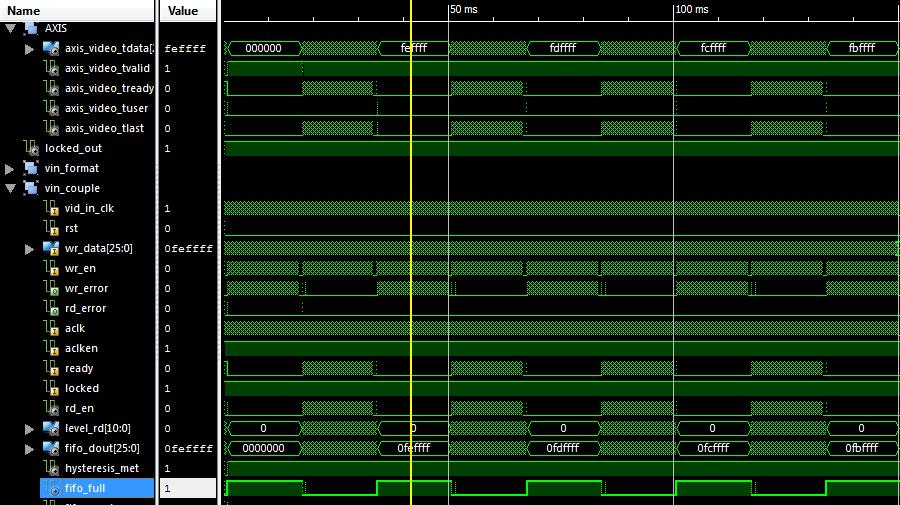

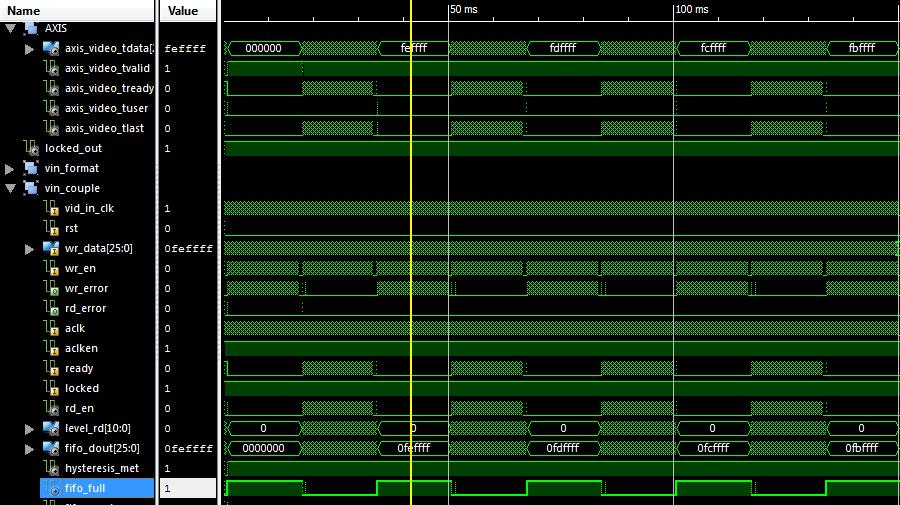

检查下面的SIM卡

Vid_in在一个完整的帧时间内获得FIFO满,但在下一个时间正常工作!

我不确定Vid_in fifo有什么问题,它有1024的默认大小。我不明白的是它在下一帧上工作正常。

注意:我尝试toforce / hack vout:lock flag up up,这使得时序/数据能够输出,但没有改变任何内部信号,同样的帧丢失发生。

没有物理屏幕可以显示这样的信号。

提前致谢,

塔里克

tb.vhd 9 KB

以上来自于谷歌翻译

以下为原文

Hello All,

I tried to operate the VDMA using my video timing/pattern generator with no luck. So I build a loopback between

- v_vid_in_axi4s

- v_axi4s_vid_out

So My IP generates Timing+DataPattern >> v_vid_in_axi4s >> AXI4-Stream >> v_axi4s_vid_out

\====== VTG (Timing)====//`

I configure the v_axi4s_vid_out (shortly: vout) parameter VTG_MASTER_SLAVE = 1 (Master)

The vout has the initialize flag always up, does not reach locked state!

But there are several abnormalities that I cannot solve, I wish someone from Xilinx Video IP team can help on this.

- Stream.TUSer misses one every two frames

- Video frames data gets alternating: one gets out correct, the next does not get out. Check the sim below

- Vid_in gets FIFO full for a complete frame time, but works correctly on the next!

I'm not sure what's wrong with the Vid_in fifo, it has the default size if 1024. What I do not understand is that it works correct on the next frame.

NB: I tried to force/hack the vout:locked flag to up, this enabled timing/data to get out, but did no change any of the internal signals, the same frame drops occur. No physical screen can display such signal.

Thanks in advance,

Tarek

tb.vhd 9 KB

举报

举报

举报

举报

举报

举报

举报

举报