刘建峰,成立,杨宁,周洋,凌新,严鸣

(1.江苏大学 电气与信息工程学院,江苏镇江 212013;2.南通职业大学

电子工程系,江苏 南通 226007;3.镇江市312国道管理站,江苏 镇江 212001)

0 引言

随着无线

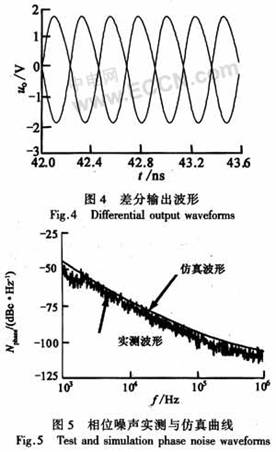

通信事业的飞速发展,产生了多种通信技术标准,诸如Bluetooth,GSM,WiFi,ZigBee等,通信频率也从数百兆赫到数千兆赫不等。从应用成本和性能角度来看,由于调谐范围宽、可靠性高的射频(RF)芯片具有广泛的使用价值,所以是当前无线通信系统的设计热点之一。而作为无线RF收发芯片的核心部件的压控振荡器(VCO),其性能好坏直接关系着RF芯片的质量。因此,多标准的通信技术对VCO提出高性能要求:获得更宽的调谐范围和更低的相位噪声(Nphase)。文献[1]介绍了一种增益可调节的CMOS LC VCO,但调节范围只有4.39~5.26 GHz,功耗为9.7 mW,在1 MHz偏频处Nphase为-113.7 dBc/Hz。文献[2]设计了一种采用正交耦合结构的CMOS VCO,其调谐范围也仅为3.6~4.9 GHz,功耗为8 mW,在1 MHz偏频处Nphase为-114 dBc/Hz。为了解决上述文献带宽较窄、Nphase值偏高的缺陷,特设计了一款0.35μm SiGe BiCMOS差分LC VCO。

举报

举报

举报

举报

举报

举报