1、引言

随着科学技术的飞速发展,航空航天设备、军用武器系统等高技术产品的复杂程度日益提高,传统的人工检测维护手段已经无法满足现代化装备的支持保障要求,自动测试系统(ATS)正逐步成为复杂系统与设备可靠运行的必要保证。

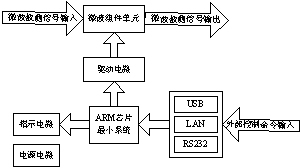

一套微波自动测试系统主要包括主控计算机、程控

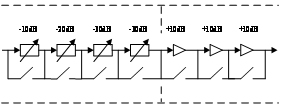

电源、信号源、频谱仪、频率计、功率计和网络分析仪等。由于微波被测信号的幅度动态范围很宽,而组成自动测试系统的仪器的种类繁多,每种仪器都有各自的功率测量范围。如果采用手动方式调整被测信号的幅度,不但会影响测量速度,而且在精密测量中,还会造成测试数据的一致性很差,甚至产生错误数据。为了解决这些微波测量中遇到的实际问题,我们设计了微波功率调整模块,将被测信号连接到微波功率调整模块的输入端,而输出端与测量仪器相连。通过主控计算机程控微波功率调整模块,对输入信号的功率进行调整。与手动调整相比,这大大提高了测试速度,具有很高的可靠性和灵活性。通过对自动、手动测试数据的分析比较发现,自动测量准确度也提高了一个数量级。

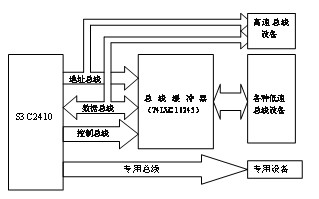

在当今的“后PC”时代,嵌入式系统以其高集成度、体积小、功耗低、可靠性高等特点,广泛应用于工业控制、无线

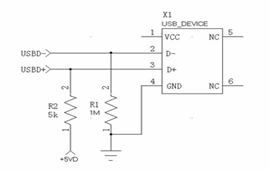

通信、网络应用等方方面面。基于该系统设计的微波功率调理模块极大的提高自动控制测量效率。同时,为了将微波功率调理模块方便、可靠、灵活的融入到各种不同自动测试系统中,我们采用USB总线、LAN总线和RS232总线控制。三种总线都是标准的计算机总线,针对不同的微波测试系统,既方便集成,又占用最少的资源。

举报

举报

举报

举报

举报

举报

举报

举报