张波,王光义,韩春艳

(1.杭州

电子科技大学 电子信息学院浙江 杭州310018;2.滨州学院山东 滨州256603)

0引言

伪噪声序列(PN序列)可应用于扩频

通信、信息加密、计算机

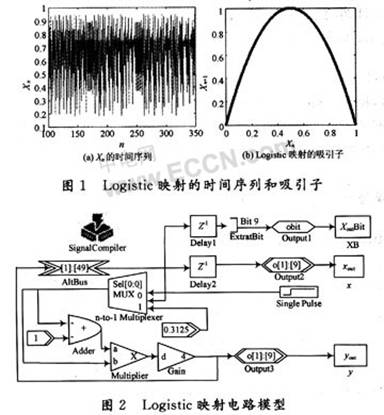

仿真等领域。PN序列发生器需要一个随机信号源和一系列的离散、量化算法及其硬件实现技术。确定性的混沌可以复制,具有长期不可预测性,且很难区分一个信号是来自于非确定性系统还是混沌系统。因此,混沌满足密码系统设计的基本原则,利用混沌系统作为PN序列的信号源已引起了国内外学者的广泛关注与研究。

基于Logis

tic映射产生PN序列已有不少研究。文献[7]利用模拟

电路研究了其实现技术,由于混沌对初值和参数的敏感性,两个模拟电路实现的PN序列,其电路参数不可能完全匹配,且受环境条件的变化而出现失配现象,很难保证保密通信或信息加密中两个PN序列的完全同步。因此,近年来开展了基于数字电路(如

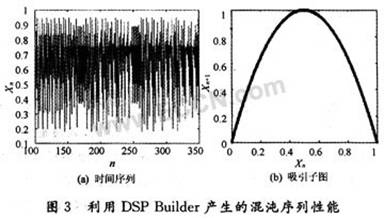

FPGA)的PN序列的实现研究,但现有的研究中大多进行仿真实验,无法保证硬件实际输出PN序列的产生及其性能的测试。为此,基于FPGA技术,利用Logistic混沌映射作为随机信号源对实现PN序列的硬件进行了深入研究,提取Logistic数值序列中二进制数的某一位bi(bi∈{0,1})为PN数字序列,实验中获得了硬件输出序列,并通过一个串口通信电路对硬件输出序列进行取样,对其进行序列统计性能分析。分析结果表明,基于Logistic的PN序列性能良好,满足PN序列测试的标准。

举报

举报

举报

举报

举报

举报

举报

举报