举报

举报

只要数据读出速度高于写入速度,就不会使图像产生突变现象,从而达到实时处理的目的。

只要数据读出速度高于写入速度,就不会使图像产生突变现象,从而达到实时处理的目的。

举报

举报

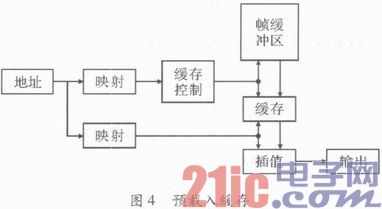

2.1 帧模块及存储模块

2.1 帧模块及存储模块 当FPGA内部的信号控制采集信号为0时,采集系统停止工作,地址发生器不计数。当其为1时,系统处于采集状态。首先只有Vsync上升沿到来后,才允许Hsync通过,从而保证采集的图像为完整的一帧图像。当Vsync上升沿到来后,对所有计数器及触发器清零。Vsync上升沿后,场消隐延时用来对Hsync计数,场消隐期后,可以采集图像。行同步计数器对Hsync进行计数。在计数的每一行中,当Hsync上升沿到来时,行消隐延时对其计数。行消隐过后,点同步计数器开始对其计数。当行同步计数停止计数时,一帧图像采集完毕,等待下一个Vsync到来。

当FPGA内部的信号控制采集信号为0时,采集系统停止工作,地址发生器不计数。当其为1时,系统处于采集状态。首先只有Vsync上升沿到来后,才允许Hsync通过,从而保证采集的图像为完整的一帧图像。当Vsync上升沿到来后,对所有计数器及触发器清零。Vsync上升沿后,场消隐延时用来对Hsync计数,场消隐期后,可以采集图像。行同步计数器对Hsync进行计数。在计数的每一行中,当Hsync上升沿到来时,行消隐延时对其计数。行消隐过后,点同步计数器开始对其计数。当行同步计数停止计数时,一帧图像采集完毕,等待下一个Vsync到来。

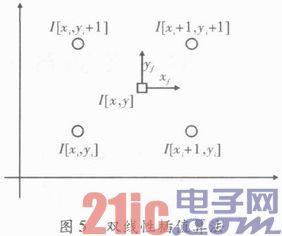

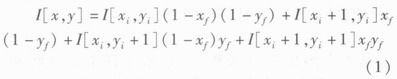

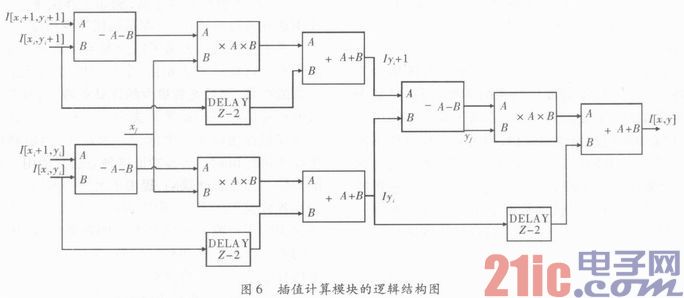

视频插值模块实现对视频按比例因子进行双线性插值放大处理。双线性插值算法的基本原理如图5所示,图中的下标i和f表示各自坐标的整数和小数部分。双线性插值是采用可分离的线性插值将4个最近的像素值组合,如式(1)。

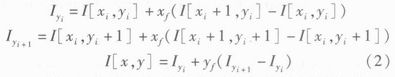

视频插值模块实现对视频按比例因子进行双线性插值放大处理。双线性插值算法的基本原理如图5所示,图中的下标i和f表示各自坐标的整数和小数部分。双线性插值是采用可分离的线性插值将4个最近的像素值组合,如式(1)。 线性插值的结果与插值的顺序无关。先进行y方向的插值,然后进行x方向的插值,所得结果相同。将式(1)进行分解,则有

线性插值的结果与插值的顺序无关。先进行y方向的插值,然后进行x方向的插值,所得结果相同。将式(1)进行分解,则有 当输入分辨率有所变化而引起缩放因子变化时,FPGA内的数字逻辑能实时计算出式(2)中的系数xf和yf。而非仅计算几种固定缩放比例,从而提高了算法模块的利用率。

当输入分辨率有所变化而引起缩放因子变化时,FPGA内的数字逻辑能实时计算出式(2)中的系数xf和yf。而非仅计算几种固定缩放比例,从而提高了算法模块的利用率。 系统包含3种不同的时钟频率:原像素点频率clkin、输出像素点频率clkout和系统主时钟频率clksys。令系统主时钟频率为4倍的原像素点频率,则使用Verilog语言及ModelSim SE 10。1 a和Quartus II仿真环境进行编译,得到双线性插值计算模块的仿真波形如图7所示。为程序书写方便,将采集的4个像素值标为a、b、c、d,经过插值模块后的输出像素值为p。从仿真波形可看出,完成了双线性插值计算模块的实现。

系统包含3种不同的时钟频率:原像素点频率clkin、输出像素点频率clkout和系统主时钟频率clksys。令系统主时钟频率为4倍的原像素点频率,则使用Verilog语言及ModelSim SE 10。1 a和Quartus II仿真环境进行编译,得到双线性插值计算模块的仿真波形如图7所示。为程序书写方便,将采集的4个像素值标为a、b、c、d,经过插值模块后的输出像素值为p。从仿真波形可看出,完成了双线性插值计算模块的实现。

举报

举报

举报

举报

更多回帖