如何降低芯片功耗目前已经成为

半导体产业的热点问题。过去,对于集成器件制造商(IDM)来说,最直接的作法就是通过先进的制程工艺和材料比如低K介质来解决,低功率设计可以通过将自己设计团队的技能和经验进行结合而实现。

然而,当进入90nm后,漏电流问题日益凸现,CMOS静态功耗骤增,功率管理开始成为一个重要的考虑因素。这种情况在65nm与45nm以下将更为严重,因为工艺节点的不断缩减导致栅极氧化层厚度越来越薄,栅极泄漏呈指数增长,最终动态功耗等于亚阈值泄漏电流,也等于栅极泄漏电流。这就迫使业界必须从IC的设计端就开始采用低功耗设计技术。

为了应对这些挑战,设计工程师们开始提倡采用复杂的时钟门

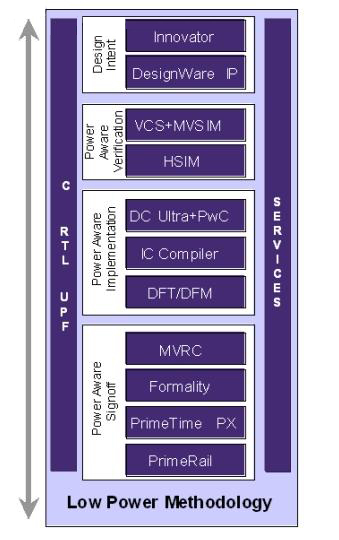

电路开关方案,从而减少了不必要的门电路开关操作。如今,为了满足功率方面的目标,设计人员运用了各种先进的低功率设计技巧,包括多阈值设计、多电压设计、动态频率电压缩放(DVFS)、时钟门控、可感知功耗的内存以及功率门控等等。

举报

举报

举报

举报

举报

举报

举报

举报