目前,无线

通信设备正朝着低电压、低功耗、低噪声和高线性度的趋势发展。混频器作为收发机中的关键模块之一,对通信设备的上述性能产生直接的影响。随着微

电子工艺的发展, CMOS器件的栅长进一步缩小,MOS器件的过驱动电压也进一步降低,这就为设计低压低功耗的射频

电路提供了可能,但是依靠减小MOS器件的栅长降低工作电压是有限的。因此,电路设计者把更多的注意力集中到电路拓扑结构上,使设计具有低压结构的射频电路成为了热门课题。

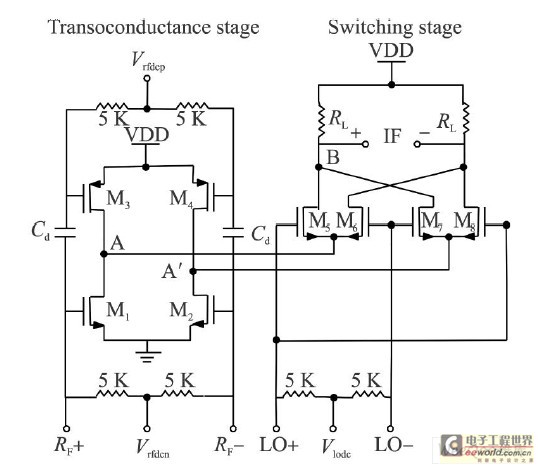

传统的Gilbert混频器由跨导级、开关级、负载级堆叠组成,其结构自下而上分别为跨导级、开关级、负载级。这种结构中,所有的直流电流都流经跨导级、开关级和负载级,跨导级与开关级电路都需要一个开启电压(VON ) ,负载级也会有一定的电压降(VRL ) , 因此,

电源电压的最小值Vdd,min = 2Von +VRL。如果采用低电源电压,这种结构不能保证所有的管子都工作在饱和区。也就是说, Gilbert混频器不能满足低电压的要求, 需要对其做出改进, 如:文献[2 - 3 ]提出省去尾电流管来减小电源电压,文献[ 4 - 11 ]用折叠结构代替堆叠结构来解决上述问题。

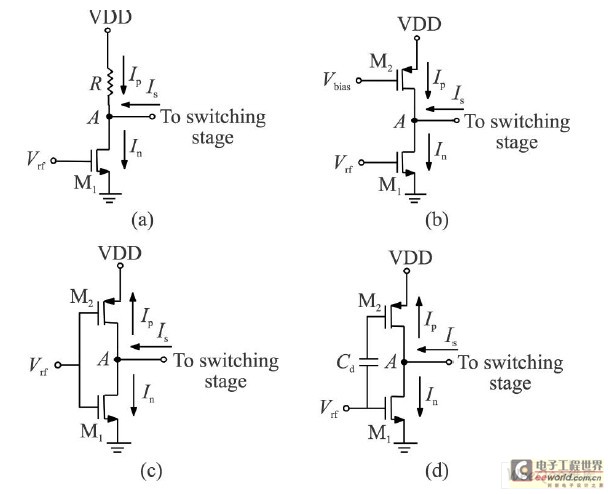

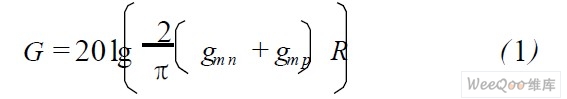

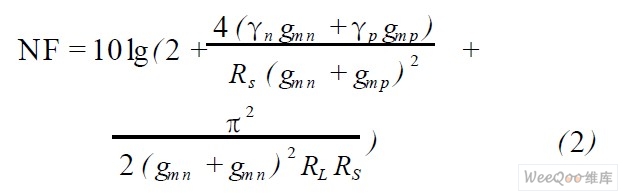

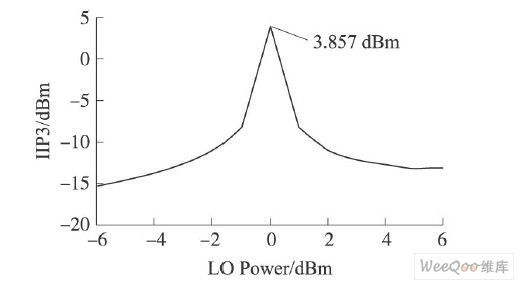

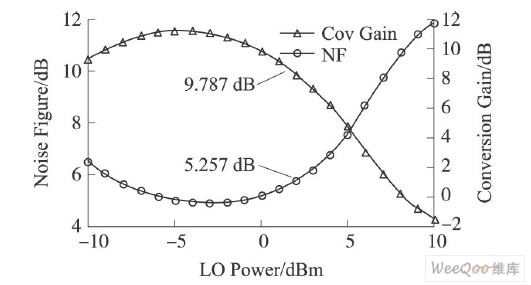

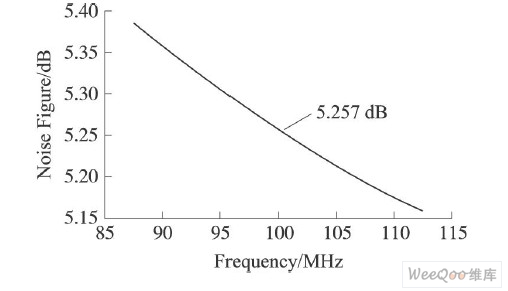

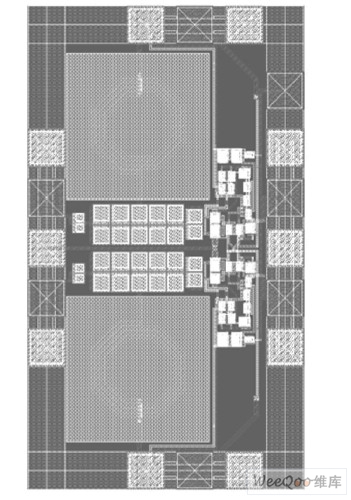

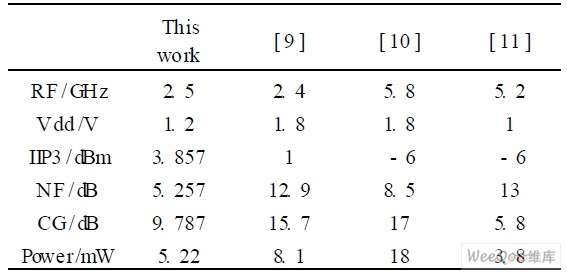

文献[ 8 ]给出了折叠结构和堆叠结构的比较,折叠结构增加了两个射频中断电路和一个耦合电容。这样对直流通道来说,跨导级与开关级、负载级的直流电路分开,两条支路相互独立,互不影响。电源电压只需提供相当于一个开启电压(Von )的值就能使跨导管与开关管都工作在各自的饱和区, 即电源电压的最小值Vdd,min = Von + VRL 。达到了低电源电压的目的。但是, 射频中断电路一般用LC 谐振网络实现,电感的使用增加了电路的版图面积和噪声。本文设计了一种新的折叠结构混频器,电路不使用具有大电感的LC谐振电路,工作于1. 2 V 电压时,得到了低电压、低功耗、低噪声和高线性度的性能。

举报

举报

举报

举报

举报

举报