手机设计工程师希望在不影响

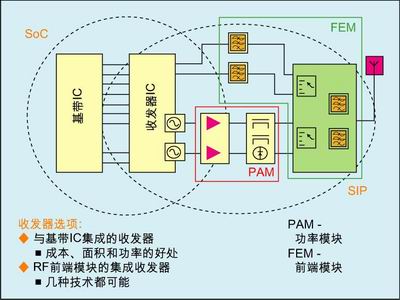

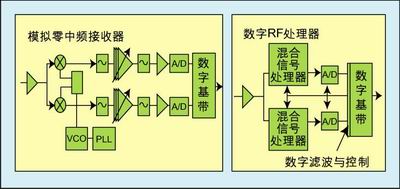

电路板面积、耗电量和成本的前提下增加更多消费者想要的功能,最有可能实现此目标的方法是从手机射频电路着手。射频电路大都是模拟器件,不但可能占用高达五成的电路板面积,耗电量也颇为可观。事实上,由于射频器件所需的电路板空间实在太大,当设计工程师为了整合蓝牙、电视、辅助全球定位系统(A-GPS)、无线网络或其它功能而必须在手机中增加无线电电路时,总会发现除了加大产品体积外几乎别无选择。另外,增加射频器件必然会增加耗电量和成本。

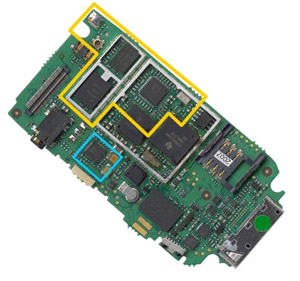

图1:黄线部分代表的射频收发相关功能约占

图1:黄线部分代表的射频收发相关功能约占

手机电路板器件总数的三分之一。

要解决这个两难的困境,关键在于不增加器件就能扩大手机功能的技术,而且要尽量提高核心器件的工作效率,让手机增加很少的电路板面积、耗电量和成本就能执行更多的无线电操作。

举报

举报

举报

举报

举报

举报