很多人都说,高速

电路看着比普通的电路的电路结构简单,但是为什么都说很难,说这话的工程师可能还没有深入的了解高速电路的特点。没错,在做低速电路的时候,总想着要做电路匹配等等,高速电路相对来讲确实简单,不是两颗芯片中间加两颗AC耦合电容直接相连,就是一颗芯片与连接器中间加两颗AC耦合电容直接相连。但是不要看着结构简单,因为在高速电路中,电路已经不是简单的电路,电容也不是简单的一颗电容啦,这一颗电容优化不好,可能就会导致你整个高速电路设计失败。

在高速串行链路中,为了让工作在不同电压下的发送器和接收器能够连接(也许是为了不影响各自buffer模拟电路部分的静态工作点),需要在通路中加入AC耦合电容,但是AC耦合电容自身和焊接电容的焊盘会给通路带来阻抗的不连续性,这在设计中都需要仔细考虑。

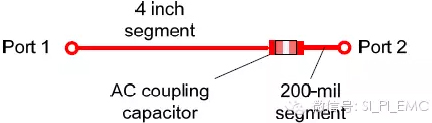

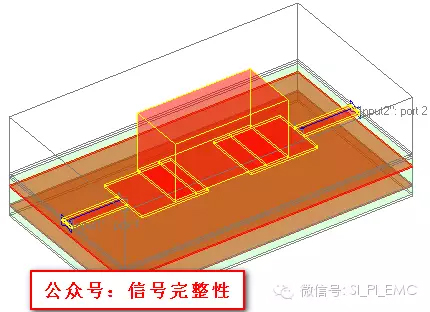

以一个典型的通路作为实例案例来研究这个问题

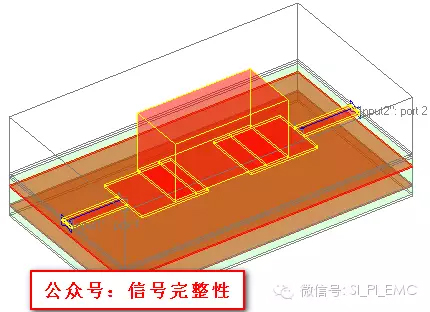

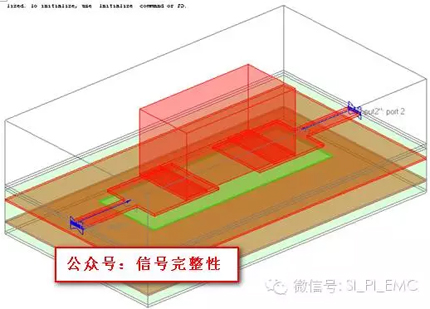

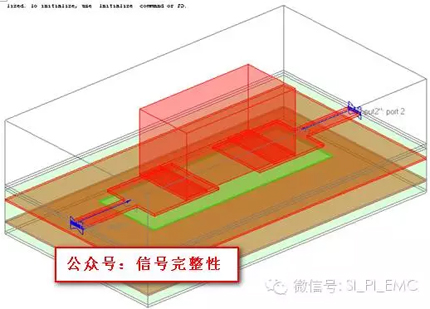

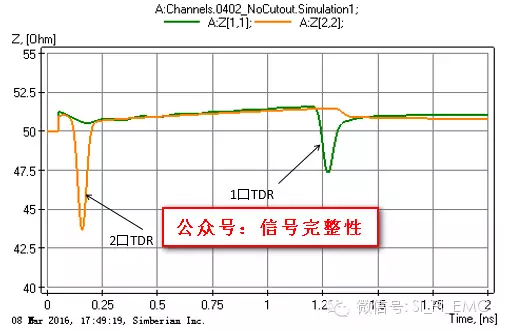

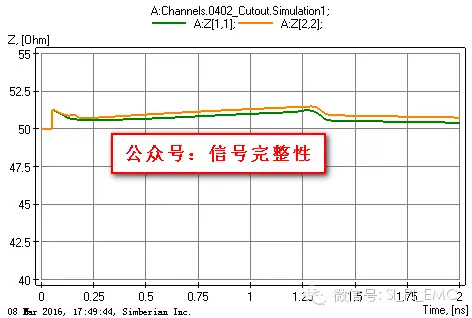

当信号传到AC耦合电容处,由于焊盘的面积和电容两端的引脚比较大,这个点的寄生电容必然很大,最终在阻抗曲线TDR图上对应地显示出阻抗偏小,进而导致return loss变的很大。为了让阻抗连续,减小电路的容性,提高阻抗,通常采取在电容的下方隔层参考(挖空某些层),如下图

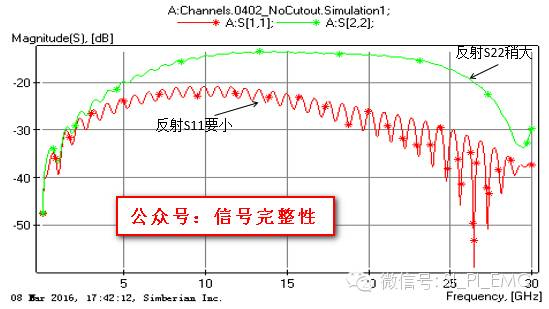

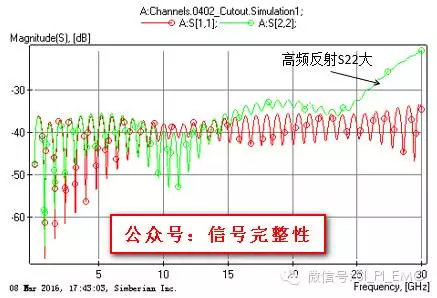

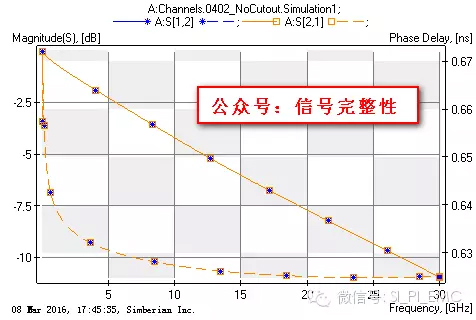

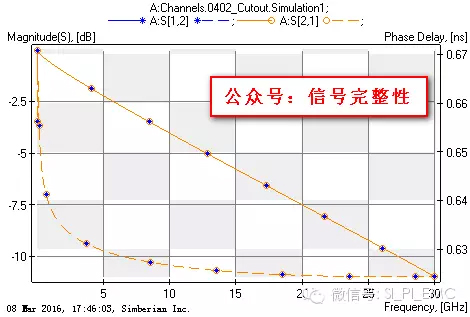

接下来,我们将通过修改前后的电容结构分别做3D电磁场

仿真,对比其处理前后的阻抗、回波损耗以及插入损耗。

举报

举报

举报

举报

举报

举报