利用通过从单一参考标准得到的频率的加、减、乘、除来产生频率的方法称为“频率合成技术”,所产生的每一频率的精度均等于参考标准的精度,并用百分数表示。频率合成方法通常有三种:间接合成、直接合成和直接数字合成(DDS)。

1、频率控制

锁相环(PPL)常用来提高频率稳定度并使微波信号源的相位噪声达到最佳。通过锁相到一个稳定的参考源-------通常是在较低频率上的温度控制晶体振荡器(TCXO),可以将后者的长期稳定度转移到微波振荡器上。

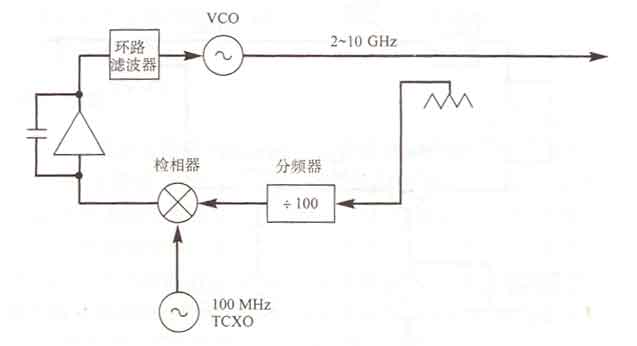

●利用谐波混频器的锁相环

上图中,10GHz输出信号的一部分连接到由100MHz TCXO激励的谐波混频器或取样器。100MHz TCXO的第100次谐波与输出信号混频,在混频器的中频(IF)端口产生与两个输入信号之间的相位差成正比的直流电压,这个电压经低通滤波再馈至积分放大器,然后再去驱动使环路闭合的调谐变容二极管。

对于这种方法进行两类观察:首先,信号源只能提供为TCXO频率的精确倍数的输出频率,即频率分辨率等于参考频率;其次,信号源的相位噪声等于参考源的相位噪声乘以在环路带宽内的输出频率与参考频率之比的平方。

举报

举报

举报

举报