射频识别即RFID技术又称

电子标签、无线射频识别,是一种

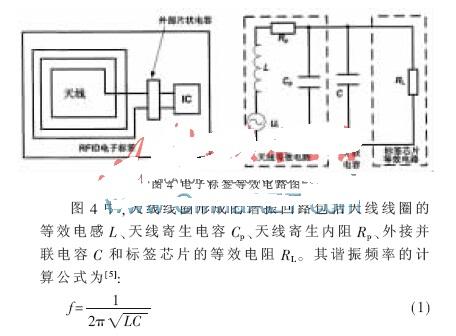

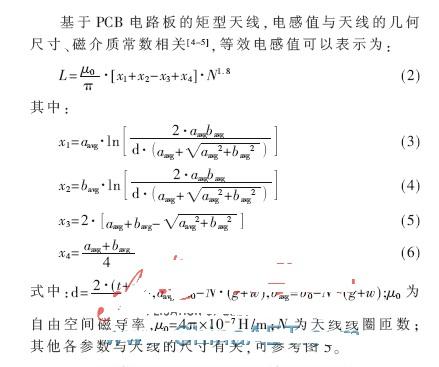

通信技术[1].RFID技术作为物联网发展的关键技术,其应用必将随着物联网的发展而扩大。常用的RFID分低频、高频、超高频3种,其中高频RFID典型工作频率为13.56 MHz,一般以无源为主。高频标签比超高频标签具有价格便宜、节省能量、穿透非金属物体力强、工作频率不受无线电频率管制约束的优势,最适合应用于含水成分较高的物体中,例如水果等。

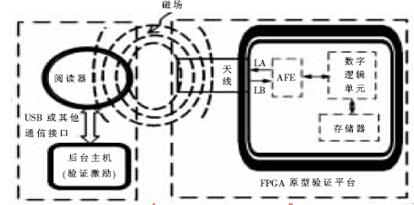

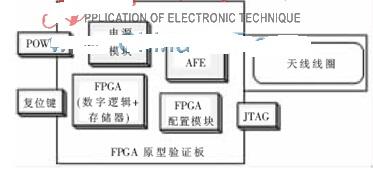

基于

FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法[2].本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。

举报

举报

举报

举报

举报

举报

举报

举报