作者:Thomas Cameron,Peadar Forbes ADI公司

引言

设想一下,某个设备可以使您在家里实现高质量的

手机接听,并允许您和您的家人无限制地使用语音和数据

通信,而且月费用很低。毫微微基站就是这样的设备,甚至还能提供更多的功能,它通常也称为毫微微蜂窝基站。当将这种小型的无线设备放置于家庭或办公室内时,它能改善本地无线覆盖率,这有望显著改变无线基础设施的产业格局。

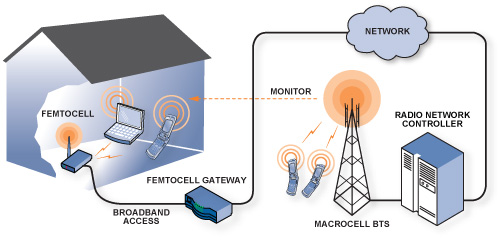

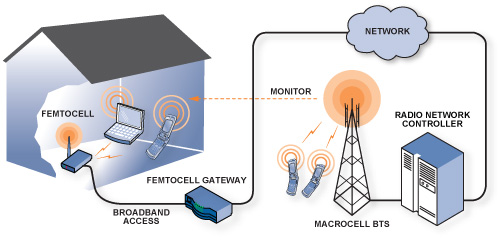

图1展示了毫微微蜂窝的概念。传统的基站提供更大范围的覆盖,而毫微微蜂窝可在更小的区域内提供无线覆盖,例如住宅。毫微微蜂窝通过用户的宽带互联网连接将手机信息流传递到网络,因而减轻无线网络的负载。毫微微蜂窝改善了网络的容量,同时减少了信号的回程路径,降低了功耗以及运营商的维护成本。它还使运营商可以参与家庭通信业务的竞争,在这个领域他们的信号覆盖通常有限。运营商可以通过增加用户的手机月费来补贴毫微微蜂窝的投入成本。当处于毫微微蜂窝区域时,所有的手机费用都被包括在家庭开销预算内,允许无限制地使用语音和数据,而不会产生很高的月费用。由于距离毫微微蜂窝很近,因此可以达到很高的连接质量,这同时可以降低手机的电池耗电量。毫微微蜂窝还克服了3G信号从基站穿透墙体的制约,因而可以实现非常高速的无线数据业务,例如浏览互联网、下载音乐以及手机接收视频流等。

图1:毫微微蜂窝基站与宏蜂窝基站的对比。

图1:毫微微蜂窝基站与宏蜂窝基站的对比。

毫微微蜂窝与Wi-Fi路由器类似,是基于经过验证的无线基础架构标准,例如UMTS、CDMA。而且它与新出现的标准兼容,利用运营商拥有的频段提供有效的、鲁棒性的无线连接。由于与现存的手机是兼容的,因此这种连接对于用户来说是透明的。不像宏蜂窝通常将数十或者数百个基站汇集到一张核心网中,毫微微蜂窝网关必须管理数千甚至数百万个的毫微微蜂窝节点。

毫微微蜂窝必须提供与手机基站相近的服务质量(QoS),并且成本也相近,这对于无线设计工程师来说是一个独特挑战。毫微微蜂窝必须提供高质量的语音服务和高速移动数据服务(EVOD和HSPA),而成本仅为宏节点的几分之一。为了解决这些挑战,毫微微蜂窝的设计必须利用低成本的制造技术和高度集成的

电路来降低调校和测试时间。由于毫微微蜂窝设备应用于家庭,因此必须体积小巧、成本低廉,以及用户可自行安装。毫微微蜂窝的发射功率很低,在100mW级别,因此其设计必须注意到无线环境问题,以便降低无线干扰,满足无线管制要求。3G毫微微蜂窝还必须能监控UMTS信道以检测附近的基站,以及检测GSM信道,这样当用户离开毫微微蜂窝区域时,可以进行恰当的网络切换。

毫微微蜂窝可以被视为由两个截然不同的功能组成:模拟前端和基带处理器。前端部分,即本文讨论的主题,将数字数据流转换成发射电路中的RF信号,在

接收链路中则相反。前端设计需要在集成度和性能之间进行折衷。尽管分立解决方案可以根据需要进行调整来提供最佳的性能,但是其成本对于毫微微蜂窝来说是不可接受的。相反,一个完全集成的解决方案可以带来最低的成本,但是性能可能达不到要求。

图2:基于ADI芯片组的毫微微蜂窝模拟前端的功能框图。

图2:基于ADI芯片组的毫微微蜂窝模拟前端的功能框图。

图2所示的是一个毫微微蜂窝设备的一个高层次功能框图,设计用于支持工作于UMTS频段的本地基站,以及监测在850MHz、900MHz、1800MHz、1900MHz和2100MHz频段的信号。混合信号前端(MxFE®)基带收发器 AD98631与 ADF4602-12集成无线收发器、ADL55423和ADL53204线性放大器、开关、滤波器和其它相关的支持电路共同组成了用于毫微微蜂窝的紧凑而高性能的前端。接下来将对图中高亮的模块进行详细描述。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报