业界普遍认为,混合波束赋形将是工作在微波和毫米波频率的5G系统的首选架构。这种架构综合运用数字 (MIMO) 和模拟波束赋形来克服高路径损耗并提高频谱效率。

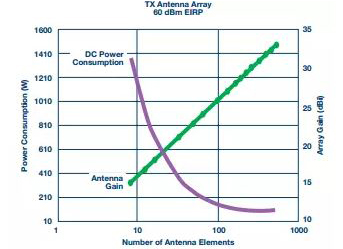

如图1所示,m个数据流的组合分割到n条RF路径上以形成自由空间中的波束,故天线

元件总数为乘积m × n。数字流可通过多种方式组合,既可利用高层MIMO将所有能量导向单个用户,也可以利用多用户MIMO支持多个用户。

图1. 混合波束赋形框图

接下来我们将考察一个简单的大规模天线阵列示例,借以探讨毫米波无线电的最优技术选择。现在深入查看毫米波系统无线电部分的框图,可以看到一个经典超外差结构完成微波信号到数字信号的变换,然后连接到多路射频信号处理路径,这里主要是运用微波移相器和衰减器来实现波束赋形。

传统上,毫米波系统是利用分立器件构建,导致其尺寸较大且成本较高。这样的系统里面的器件使用CMOS、SiGe BiCMOS和 GaAs等技术,使每个器件都能得到较优的性能。例如,数据转换器现在采用CMOS工艺开发,使采样速率达到GHz范围。上下变频和波束赋形功能可以在SiGe BiCMOS中有效实现。根据系统指标要求,可能需要基于GaAs功率放大器和低噪声放大器,但如果 SiGe BiCMOS能够满足要求,利用它将能实现较高的集成度。

对于5G毫米波系统,业界希望将微波器件安装在天线基板背面,这要求微波芯片的集成度必须大大提高。例如,中心频率为 28 GHz的天线的半波阵子间距约为5 mm。频率越高,此间距越小,芯片或封装尺寸因而成为重要考虑因素。理想情况下,单波 束的整个框图都应当集成到单个IC中;实际情形中,至少应将上下变频器和RF前端集成到单个RFIC中。集成度和工艺选择在某种程度上是由应用决定的,在下面的示例分析中我们将体会到这一点。

一个示例,分析分析

举报

举报

举报

举报