嘿,我正在为系统和编解码器生成时钟

模块预分频器(clk,//从pll输入50mhz输入

RESET_IN,

twelwe_dot_five_M,

tre_dot_one_twenty_five_M,

forty_eight_kilo_M);

输入clk;

input reset_in;

wire not_reset_in;

assign not_reset_in = ~reset_in;

输出twelwe_dot_five_M;

输出tre_dot_one_twenty_five_M; // 64fs - >单个位的时钟

输出forty_eight_kilo_M;

//样本的周期 - > iir的时钟

reg [9:0]柜台;

初始反击

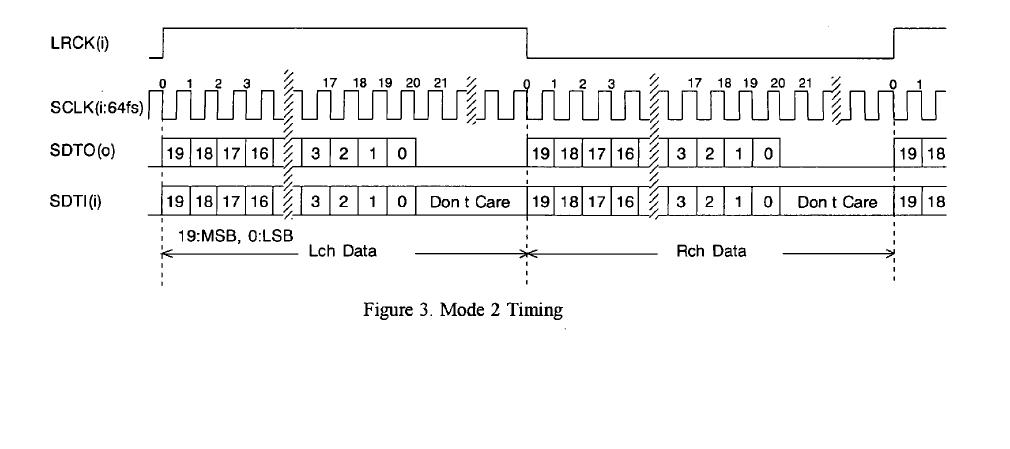

我没有使用I2S,在我将I2S模式表示为不同模式之前提到的编解码器文档中。

我只能使用我在previuos帖子中发布的比特序列。

1)SERIAL_TO_PARALLEL

我发布了模拟器的输出

您可以看到的问题是,即使在重置之后,par_output的所有位都是x。

我重新发布了代码

module ser_to_par(//串行并行转换器

clk,// 3,125Mhz 64fs

ser_in,//串行数据输入

RESET_IN,

par_out

);

输入clk;

输入ser_in;

input reset_in;

wire not_reset_in;

assign not_reset_in = ~reset_in;

输出[7:0] par_out;

reg [7:0] temporany_par;

reg [7:0] par_out;

reg [5:0]计数;

总是@(posedge clk或posedge not_reset_in)

开始

如果(not_reset_in == 1)开始

temporany_par

2)PARALLEL_TO_SERIAL

模拟输出是

奇怪的行为可能是因为我使用了一个糟糕的测试wawefile,我重新创建它改变每个32clk节拍par_in似乎工作但问题是第一个样本没问题,但第二个没有!

(看看wawe的结尾)我不知道为什么。

你可以用更长的时间模拟吗?

我尝试过很长时间的测试,但是对于modelsim的学生版我不能做更多

代码是

模块par_to_ser(// paralll到串行转换器

clk,// 3,125mhz 64fs

RESET_IN,

par_in,

ser_out

);

输入clk;

input reset_in;

输入[15:0] par_in;

输出ser_out;

reg ser_out;

wire not_reset_in;

assign not_reset_in = ~reset_in;

reg [5:0]柜台;

最初开始

ser_out15)开始

ser_out

以上来自于谷歌翻译

以下为原文

Hey, I'm generating clock for system and codec with

module prescaler(clk, //clock a 50mhz input from pll reset_in, twelwe_dot_five_M, tre_dot_one_twenty_five_M, forty_eight_kilo_M);input clk;input reset_in;wire not_reset_in;assign not_reset_in=~reset_in;output twelwe_dot_five_M;output tre_dot_one_twenty_five_M;//64fs -->clock of a single bitoutput forty_eight_kilo_M; // sample's period --> clock of iirreg [9:0] counter;initial counter<=0;always @(posedge clk or posedge not_reset_in)//reset active lowif (not_reset_in==1'b1) counter <=10'b0;else begincounter <=counter + 1'b1;endassign twelwe_dot_five_M = counter[1];//mclk master clock codecassign tre_dot_one_twenty_five_M = counter[3]; // sclkassign forty_eight_kilo_M = counter[9]; //lrckendmodule

I'm not using I2S, in the codec documentation i allegated before I2S mode is represented as a different mode. I can use only the bit sequence i posted in the previuos post.

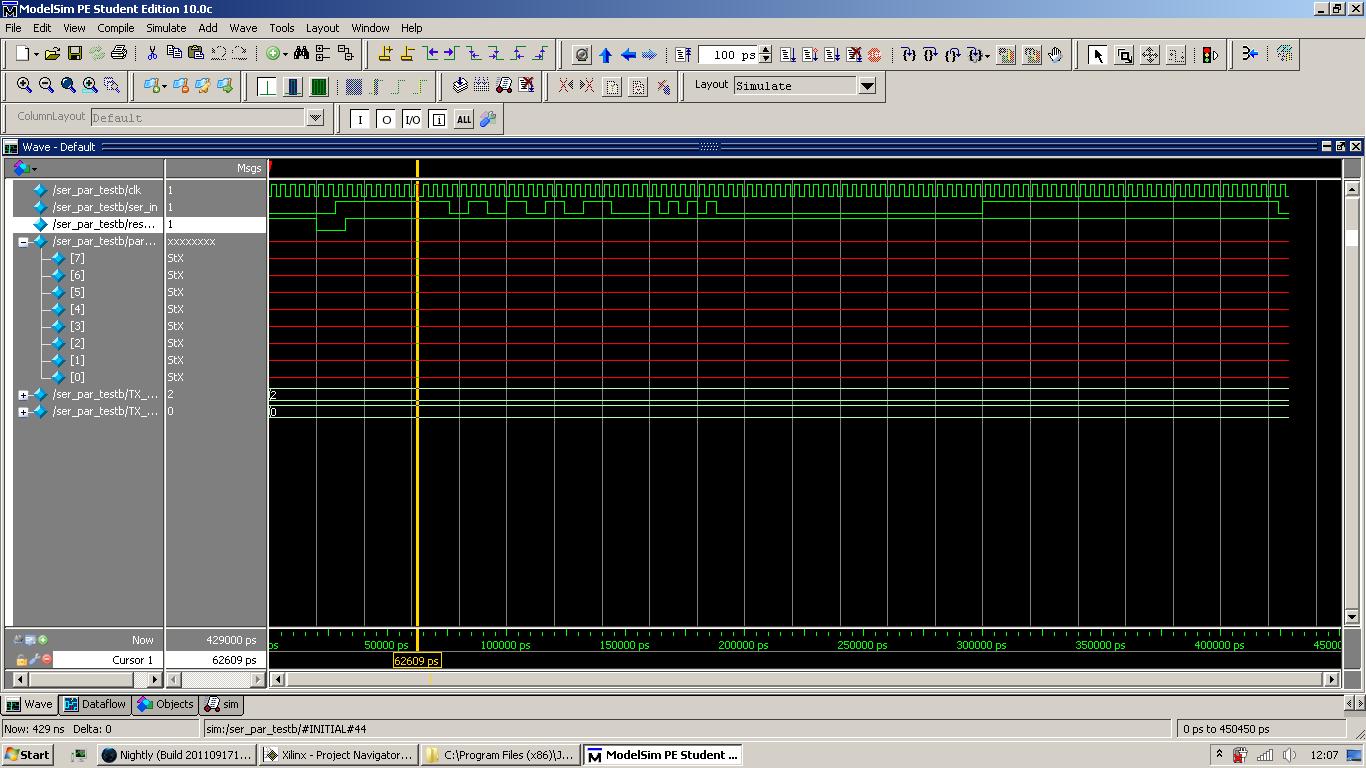

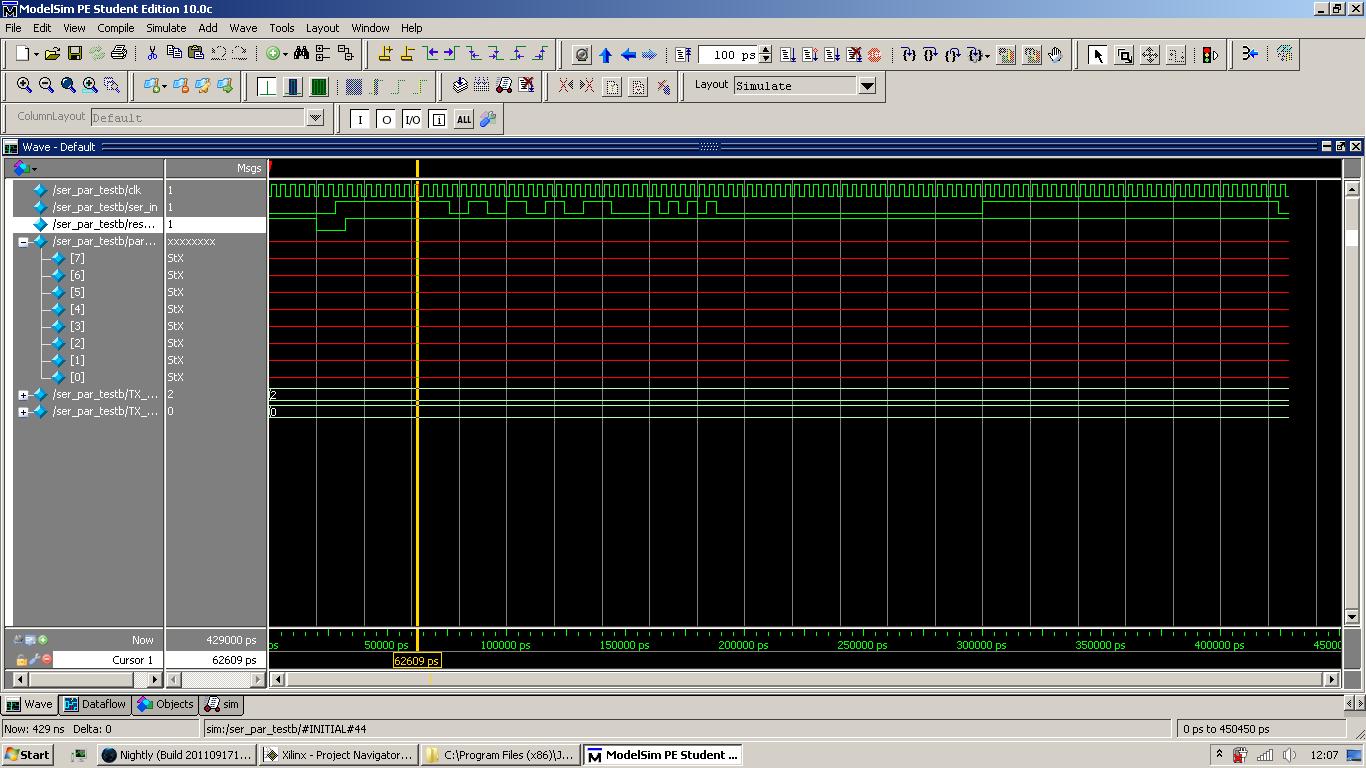

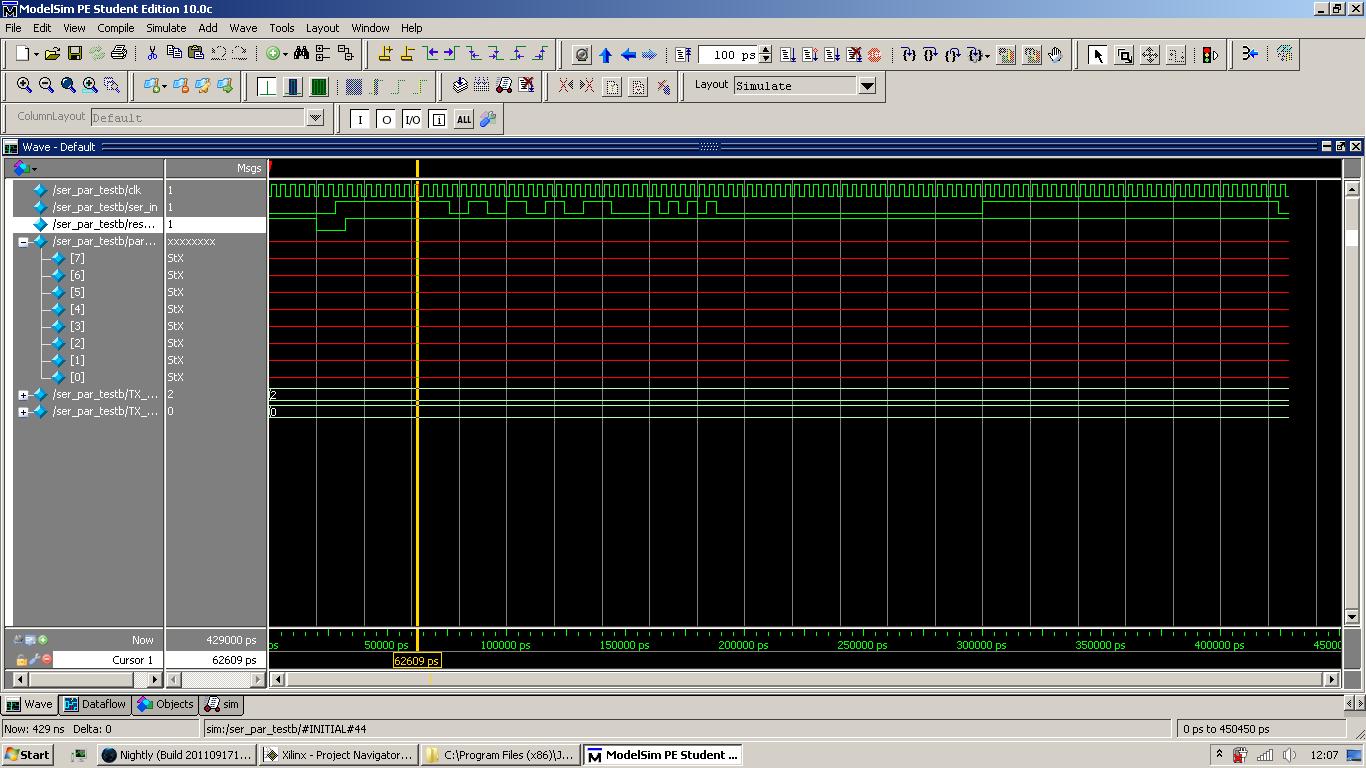

1)SERIAL_TO_PARALLEL

I post the output of simulator

The problem as you can see is that all the bits of the par_output are x , even after a reset.

I repost the code

module ser_to_par( // serial parallel converteerclk, // 3,125Mhz 64fsser_in,// serial data inputreset_in,par_out);input clk;input ser_in;input reset_in;wire not_reset_in;assign not_reset_in=~reset_in;output [7:0] par_out;reg [7:0] temporany_par;reg [7:0] par_out;reg[5:0] count;always @ (posedge clk or posedge not_reset_in)begin if(not_reset_in==1)begin temporany_par<=0;endelse begin if(count<5'b01000) begintemporany_par <= {temporany_par[8-2:0],ser_in};par_out = temporany_par;end count<=count +1'b1;endendendmodule

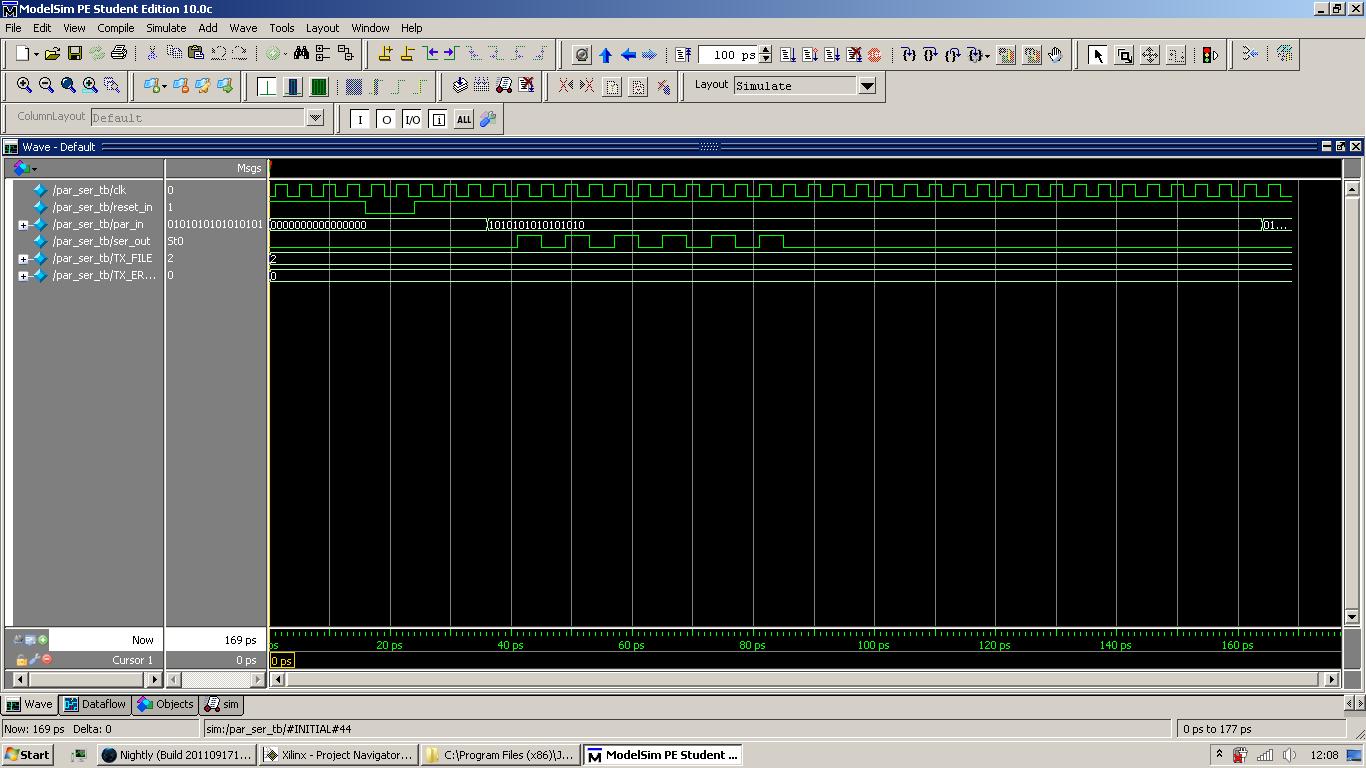

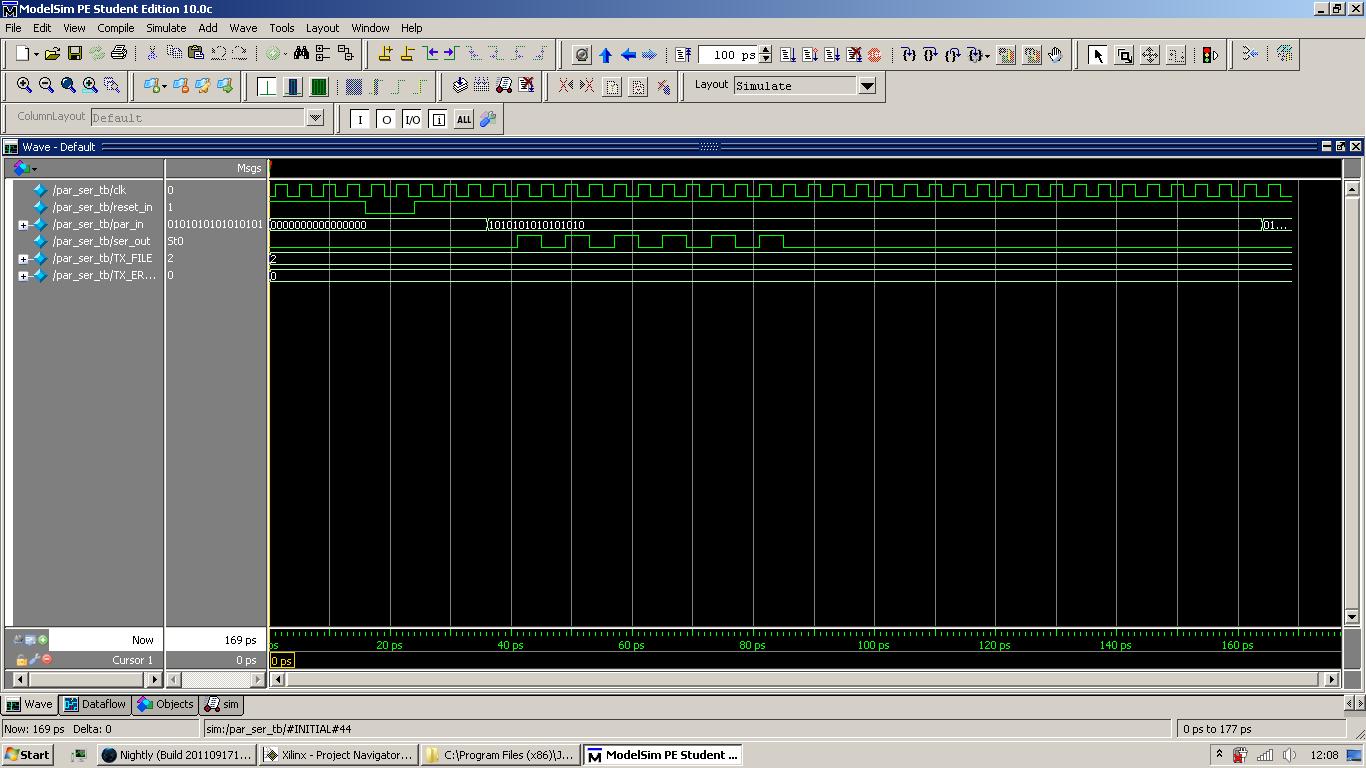

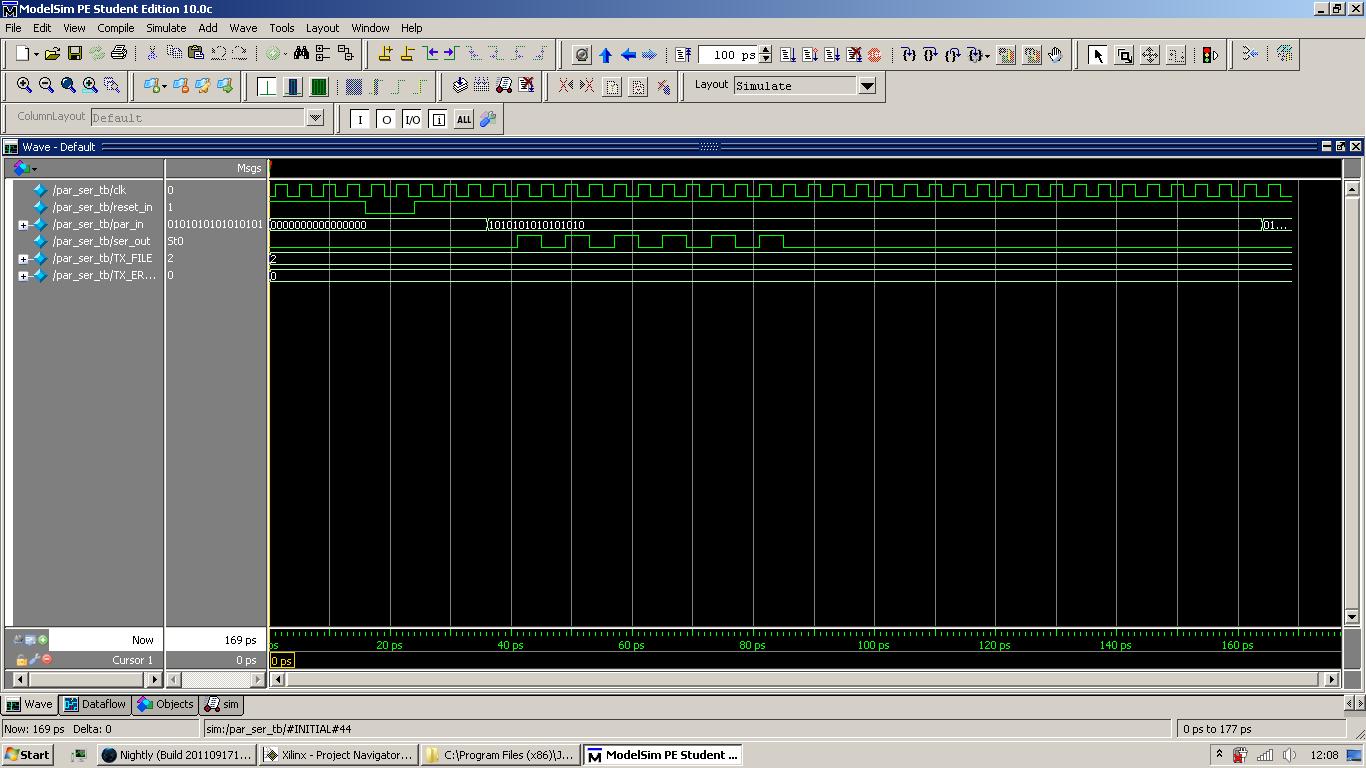

2) PARALLEL_TO_SERIAL

The simulation output is

Strange behaviuor was maybe because I used a bad test wawefile, I've recreated it changing every 32clk beats par_in and seems to work but a problem is that the first sample go ok but the second not! ( look at the end of the wawe) and I don't know why. Could you simulate with a longer time? I've tryed with a very long test waweform but with the student version of modelsim I can't do more

code is

module par_to_ser( // paralll to serial converterclk, // 3,125mhz 64fsreset_in,par_in,ser_out);input clk;input reset_in;input [15:0] par_in;output ser_out;reg ser_out;wire not_reset_in;assign not_reset_in=~reset_in;reg [5:0] counter;initial beginser_out<=0;counter<=0;endalways@(posedge clk or posedge not_reset_in) beginif(not_reset_in==1) begincounter<=0;ser_out<=0;endelse beginif(counter<=15) beginser_out<=par_in[15-counter]; // MSBendelse if(counter>15) beginser_out<=0; // 16 bit don't careendcounter<=counter+1'b1;endendendmodule

嘿,我正在为系统和编解码器生成时钟

模块预分频器(clk,//从pll输入50mhz输入

RESET_IN,

twelwe_dot_five_M,

tre_dot_one_twenty_five_M,

forty_eight_kilo_M);

输入clk;

input reset_in;

wire not_reset_in;

assign not_reset_in = ~reset_in;

输出twelwe_dot_five_M;

输出tre_dot_one_twenty_five_M; // 64fs - >单个位的时钟

输出forty_eight_kilo_M;

//样本的周期 - > iir的时钟

reg [9:0]柜台;

初始反击

我没有使用I2S,在我将I2S模式表示为不同模式之前提到的编解码器文档中。

我只能使用我在previuos帖子中发布的比特序列。

1)SERIAL_TO_PARALLEL

我发布了模拟器的输出

您可以看到的问题是,即使在重置之后,par_output的所有位都是x。

我重新发布了代码

module ser_to_par(//串行并行转换器

clk,// 3,125Mhz 64fs

ser_in,//串行数据输入

RESET_IN,

par_out

);

输入clk;

输入ser_in;

input reset_in;

wire not_reset_in;

assign not_reset_in = ~reset_in;

输出[7:0] par_out;

reg [7:0] temporany_par;

reg [7:0] par_out;

reg [5:0]计数;

总是@(posedge clk或posedge not_reset_in)

开始

如果(not_reset_in == 1)开始

temporany_par

2)PARALLEL_TO_SERIAL

模拟输出是

奇怪的行为可能是因为我使用了一个糟糕的测试wawefile,我重新创建它改变每个32clk节拍par_in似乎工作但问题是第一个样本没问题,但第二个没有!

(看看wawe的结尾)我不知道为什么。

你可以用更长的时间模拟吗?

我尝试过很长时间的测试,但是对于modelsim的学生版我不能做更多

代码是

模块par_to_ser(// paralll到串行转换器

clk,// 3,125mhz 64fs

RESET_IN,

par_in,

ser_out

);

输入clk;

input reset_in;

输入[15:0] par_in;

输出ser_out;

reg ser_out;

wire not_reset_in;

assign not_reset_in = ~reset_in;

reg [5:0]柜台;

最初开始

ser_out15)开始

ser_out

以上来自于谷歌翻译

以下为原文

Hey, I'm generating clock for system and codec with

module prescaler(clk, //clock a 50mhz input from pll reset_in, twelwe_dot_five_M, tre_dot_one_twenty_five_M, forty_eight_kilo_M);input clk;input reset_in;wire not_reset_in;assign not_reset_in=~reset_in;output twelwe_dot_five_M;output tre_dot_one_twenty_five_M;//64fs -->clock of a single bitoutput forty_eight_kilo_M; // sample's period --> clock of iirreg [9:0] counter;initial counter<=0;always @(posedge clk or posedge not_reset_in)//reset active lowif (not_reset_in==1'b1) counter <=10'b0;else begincounter <=counter + 1'b1;endassign twelwe_dot_five_M = counter[1];//mclk master clock codecassign tre_dot_one_twenty_five_M = counter[3]; // sclkassign forty_eight_kilo_M = counter[9]; //lrckendmodule

I'm not using I2S, in the codec documentation i allegated before I2S mode is represented as a different mode. I can use only the bit sequence i posted in the previuos post.

1)SERIAL_TO_PARALLEL

I post the output of simulator

The problem as you can see is that all the bits of the par_output are x , even after a reset.

I repost the code

module ser_to_par( // serial parallel converteerclk, // 3,125Mhz 64fsser_in,// serial data inputreset_in,par_out);input clk;input ser_in;input reset_in;wire not_reset_in;assign not_reset_in=~reset_in;output [7:0] par_out;reg [7:0] temporany_par;reg [7:0] par_out;reg[5:0] count;always @ (posedge clk or posedge not_reset_in)begin if(not_reset_in==1)begin temporany_par<=0;endelse begin if(count<5'b01000) begintemporany_par <= {temporany_par[8-2:0],ser_in};par_out = temporany_par;end count<=count +1'b1;endendendmodule

2) PARALLEL_TO_SERIAL

The simulation output is

Strange behaviuor was maybe because I used a bad test wawefile, I've recreated it changing every 32clk beats par_in and seems to work but a problem is that the first sample go ok but the second not! ( look at the end of the wawe) and I don't know why. Could you simulate with a longer time? I've tryed with a very long test waweform but with the student version of modelsim I can't do more

code is

module par_to_ser( // paralll to serial converterclk, // 3,125mhz 64fsreset_in,par_in,ser_out);input clk;input reset_in;input [15:0] par_in;output ser_out;reg ser_out;wire not_reset_in;assign not_reset_in=~reset_in;reg [5:0] counter;initial beginser_out<=0;counter<=0;endalways@(posedge clk or posedge not_reset_in) beginif(not_reset_in==1) begincounter<=0;ser_out<=0;endelse beginif(counter<=15) beginser_out<=par_in[15-counter]; // MSBendelse if(counter>15) beginser_out<=0; // 16 bit don't careendcounter<=counter+1'b1;endendendmodule

举报

举报

举报

举报

举报

举报