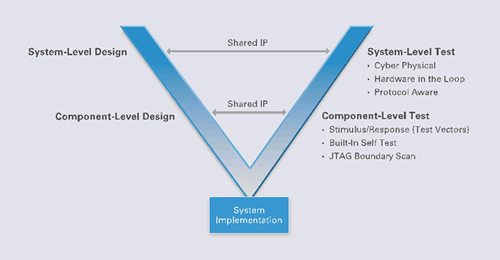

很久以前人们便预测,未来的设计与测试会相互结合--在完整的系统设计流程中,这两种一向井水不犯河水的功能会整合在一起。只要纳入符合设计的测试定义与操作,整合两者的好处可说是显而易见,不仅能缩短上市时间,还可以提高整体品质。这些测试台可于系统设计流程中重复使用,因其包含模拟、操作,以至于最终系统部署等步骤。

为整合设计与测试,尤其是针对射频(RF)

通信等较为复杂的功能,系统设计软件与所选语言必须能同时针对测试与操作,在整个设计周期中有效运作。

一般而言,用于模拟/设计系统的工具与技术不同于运用在操作系统的工具与技术。此外,设计/操作专用的工具和语言也不同于测试工具和语言。这样一来,便需要不同的团队,各有各的职责与工具,所以不仅会提高沟通的难度,也会因此降低设计与测试中重复使用程序码的流畅度。

以上这些情况都会有损设计/测试相互整合的好处,因此理想的系统设计软件一定要提供可同时用于模拟、操作、测试的单一语言,并且尽量重复使用所有的设计函式与相位。

举报

举报

举报

举报

举报

举报

举报

举报