普通光耦的阻抗匹配问题参考我之前的那篇文章《普通光耦 上下拉电阻选择》。

现如今通讯速率越来越快的当下,普通光耦在单纯的只接电阻情况下,上升时间Tr有20us左右,这将无法适用于高速通讯。然而高速光耦在使用过程中若阻抗选取不当也会导致上升延迟过大,电平拉不到底等问题。

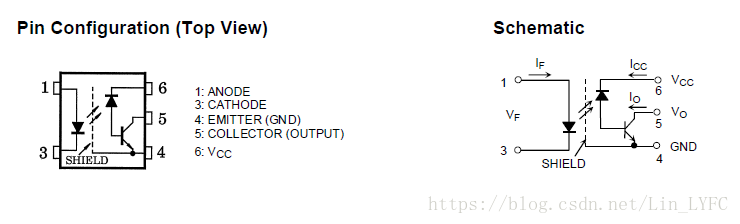

高速光耦TLP109内部构造如下图所示:

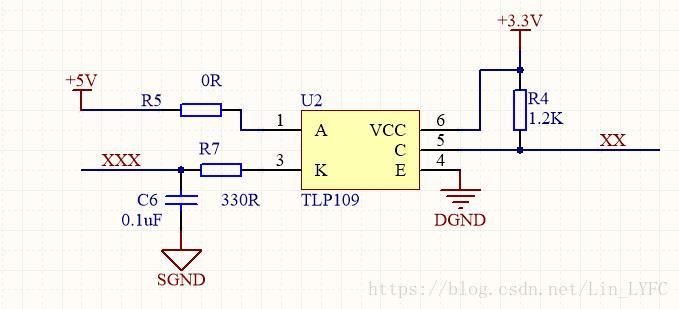

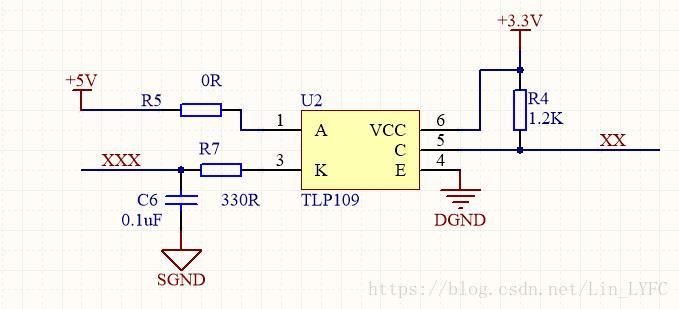

以下是一个简单使用的

电路(C6不贴,除非干扰很大,信号宽度够且能忍受增加信号延迟):

参考手册给出的上升延迟为2us左右,下面列举一些问题。

R4/R7比值过大:

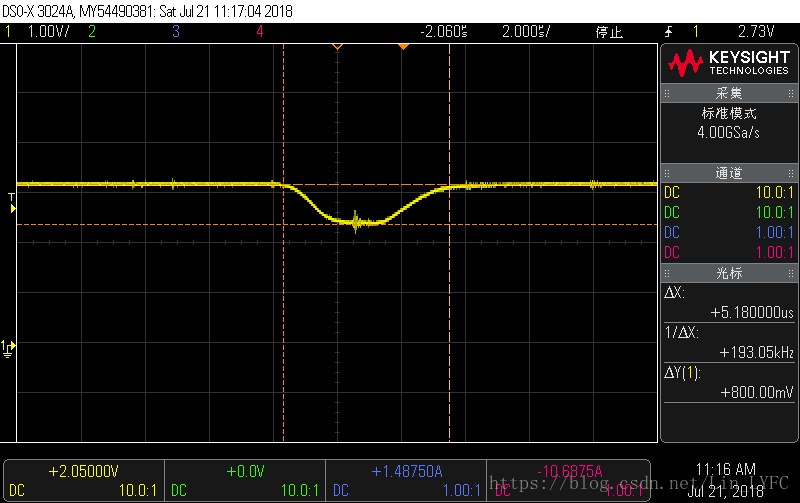

R4/R7比值过小:

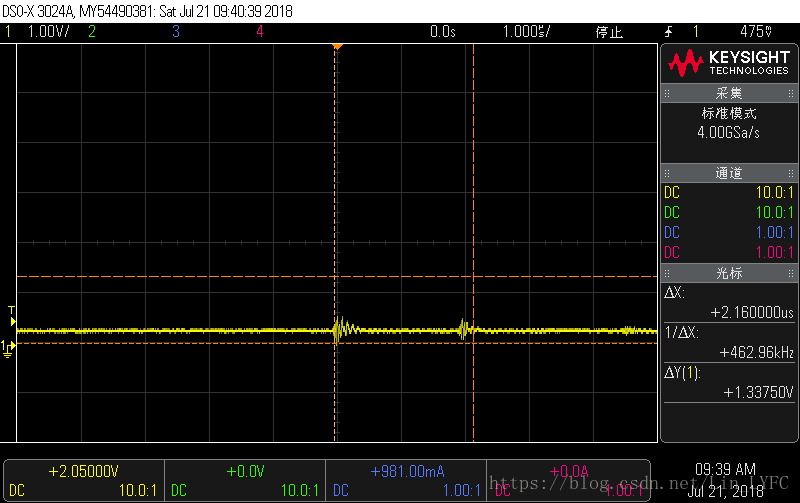

当时的信号宽度只有4us不到,做了几组实验得出结论:

A.当输入侧电阻为330Ω时,输出侧电阻应该选取1K~2.2K能保证输出的波形正确,能被检测到。

B.当输入侧电阻为1K时,输出侧电阻应该选取3K~8K能保证输出的波形正确,能被检测到。

1.增大输出侧电阻会减小上升时间(tr),但是增大的输出侧电阻也会增大下降时间(tf)。

2.过大的输出电阻会导致三极管的输出电压静态工作点过低,过小的输出侧电阻会导致光耦电流转换率(CTR)不足,导致三极管导通压降过大,输出低电平过高。

3.适度增大输入电阻,可以增大输出电阻的选取范围。

4.过大的输入电阻会导致电流转换率(CTR)不足,导致三极管导通压降过大,输出低电平过高。过小的输入电阻会导致静态时的噪声等因素会导致输出侧导通,无法传送信号。

5.输入侧一般不加电容,增加电容会起到滤波作用,出现类似R4/R7比值过小的图像效果(图没找到)。