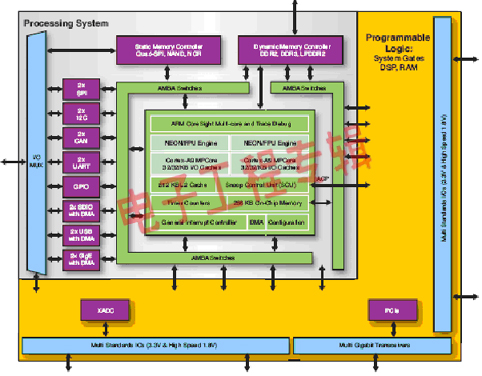

赛灵思处理平台副总裁Larry Getman表示:“从最根本的层次来说,Zynq-7000 EPP应该算是一类全新的半导体产品。它既不是单纯的处理器,也不是单纯的FPGA。我们的产品是两者的完美结合,正因如此我们才能够帮助您消除现有解决方案的局限性,尤其针对双芯片解决方案和ASIC。

Getman称当前大多数电子系统都是将一个FPGA和一个独立处理器或者一个带有片上处理器的ASIC在同一个PCB上配合使用。赛灵思的最新产品可支持使用这类双芯片解决方案的公司利用一个Zynq-7000芯片来构建下一代系统,节省了物料成本和PCB空间,并且降低了总体功耗预算。由于处理器和FPGA在相同的架构上,因此性能也得到了大幅提升。

Getman表示Zynq-7000 EPP将会加快从ASIC向FPGA的市场迁移。采用最新制造工艺实施ASIC过于昂贵并且对大多数应用来说风险太大。因此,越来越多的公司青睐于FPGA。许多尝试坚守旧ASIC方法的公司采用旧的制造工艺来实施他们的设计,分析师称之为“价值认知型片上系统ASIC”。然而ASIC依旧需要较长的设计周期并且存在重新设计(respin)的风险,这样一来费用将会非常昂贵并且可能还会延迟产品的上市时间。Getman说:“与旧技术相比,借助采用28 nm技术的Zynq-7000 EPP,器件的可编程逻辑部分并不存在尺寸或性能损耗的问题,您还可在处理子系统中获得硬化28 nm片上系统的附加优势。凭借不到15美元的起始售价,我们使设计那些产量并非很大的ASIC在成本和风险上都不再划算。您可以即刻让您的软硬件团队开工,而那些死守ASIC的设计团队就很难做到这一点。”

Getman表示自从赛灵思去年推出这款架构以来,市场对Zynq-7000 EPP的兴趣和需求非常强烈。经选择出的一部分早期试用客户(alpha customer)已开始对将使用Zynq-7000器件的系统进行原型设计。该技术非常令人兴奋。”

赛灵思处理平台副总裁Larry Getman表示:“从最根本的层次来说,Zynq-7000 EPP应该算是一类全新的半导体产品。它既不是单纯的处理器,也不是单纯的FPGA。我们的产品是两者的完美结合,正因如此我们才能够帮助您消除现有解决方案的局限性,尤其针对双芯片解决方案和ASIC。

Getman称当前大多数电子系统都是将一个FPGA和一个独立处理器或者一个带有片上处理器的ASIC在同一个PCB上配合使用。赛灵思的最新产品可支持使用这类双芯片解决方案的公司利用一个Zynq-7000芯片来构建下一代系统,节省了物料成本和PCB空间,并且降低了总体功耗预算。由于处理器和FPGA在相同的架构上,因此性能也得到了大幅提升。

Getman表示Zynq-7000 EPP将会加快从ASIC向FPGA的市场迁移。采用最新制造工艺实施ASIC过于昂贵并且对大多数应用来说风险太大。因此,越来越多的公司青睐于FPGA。许多尝试坚守旧ASIC方法的公司采用旧的制造工艺来实施他们的设计,分析师称之为“价值认知型片上系统ASIC”。然而ASIC依旧需要较长的设计周期并且存在重新设计(respin)的风险,这样一来费用将会非常昂贵并且可能还会延迟产品的上市时间。Getman说:“与旧技术相比,借助采用28 nm技术的Zynq-7000 EPP,器件的可编程逻辑部分并不存在尺寸或性能损耗的问题,您还可在处理子系统中获得硬化28 nm片上系统的附加优势。凭借不到15美元的起始售价,我们使设计那些产量并非很大的ASIC在成本和风险上都不再划算。您可以即刻让您的软硬件团队开工,而那些死守ASIC的设计团队就很难做到这一点。”

Getman表示自从赛灵思去年推出这款架构以来,市场对Zynq-7000 EPP的兴趣和需求非常强烈。经选择出的一部分早期试用客户(alpha customer)已开始对将使用Zynq-7000器件的系统进行原型设计。该技术非常令人兴奋。”

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报