你好,我是学生。

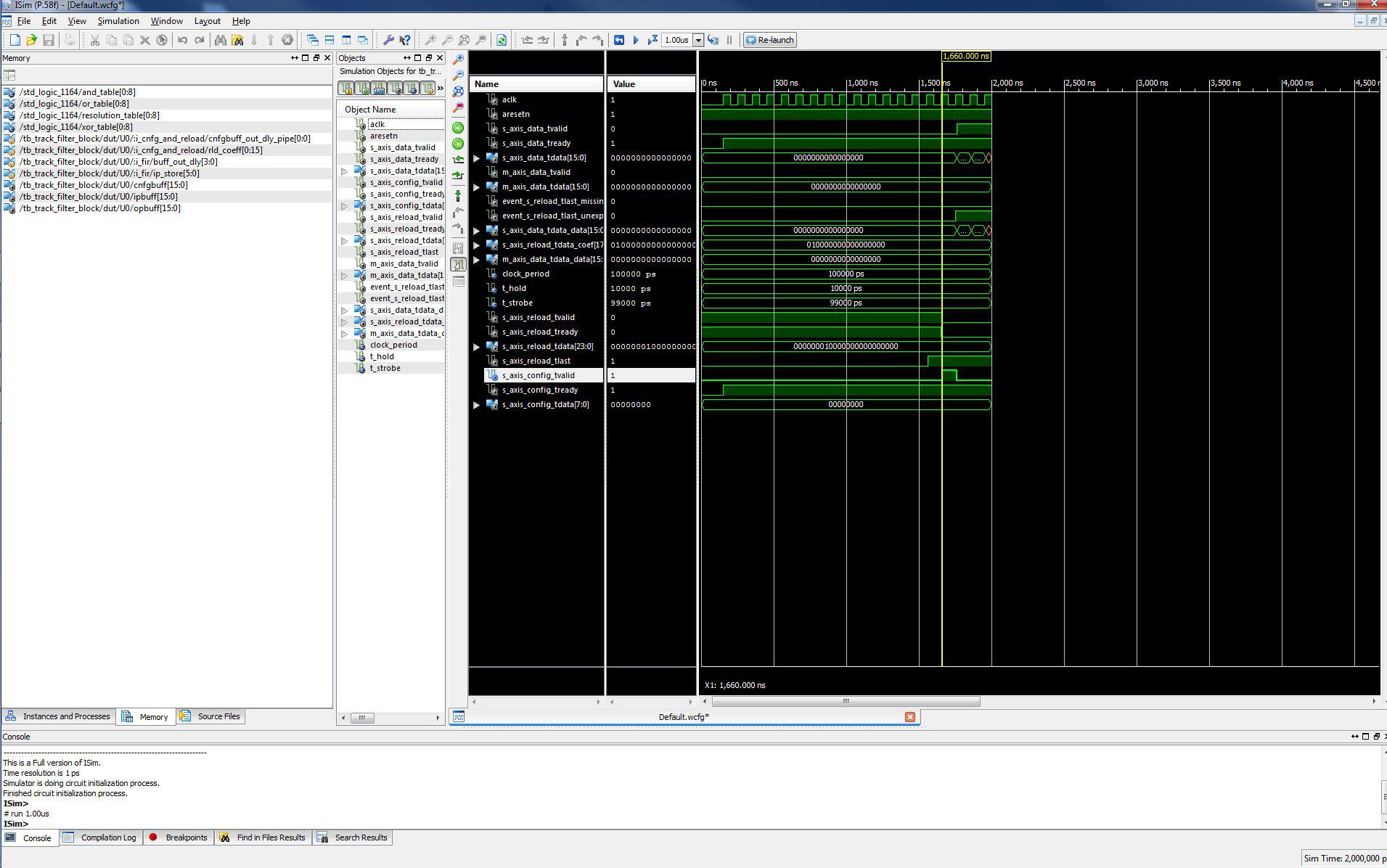

现在我设计了一个带有3个系数集的滤波器,我想在FIR Compiler 6.3中使用重载功能。系统可以在3个样本频率下工作,所以滤波器有3个系数集。

当选择频率样本时,我想重新加载系数。

系数在* .coe文件中,重新加载时,系数数据如何下降到核心?

以及如何计算重装槽?

我正在寻找你的回复!

我的邮箱是wuyanbei24@gmial.com。

谢谢!

以上来自于谷歌翻译

以下为原文

hello i am a student.

now i am design a filter wtih 3 coefficient sets,i want to use reload funtion in FIR Compiler 6.3 .the system can work in 3 sample feequency so the filter have 3 coefficeint sets. when chose the sample frequey, i want to reload the coefficeints.

the coefficeitns are in *.coe file, when reloading,how the coefficient data downto the core?

and how to caculae the reload slots?

i am looking forword your reply!

my mail is wuyanbei24@gmial.com.

thank you!

你好,我是学生。

现在我设计了一个带有3个系数集的滤波器,我想在FIR Compiler 6.3中使用重载功能。系统可以在3个样本频率下工作,所以滤波器有3个系数集。

当选择频率样本时,我想重新加载系数。

系数在* .coe文件中,重新加载时,系数数据如何下降到核心?

以及如何计算重装槽?

我正在寻找你的回复!

我的邮箱是wuyanbei24@gmial.com。

谢谢!

以上来自于谷歌翻译

以下为原文

hello i am a student.

now i am design a filter wtih 3 coefficient sets,i want to use reload funtion in FIR Compiler 6.3 .the system can work in 3 sample feequency so the filter have 3 coefficeint sets. when chose the sample frequey, i want to reload the coefficeints.

the coefficeitns are in *.coe file, when reloading,how the coefficient data downto the core?

and how to caculae the reload slots?

i am looking forword your reply!

my mail is wuyanbei24@gmial.com.

thank you!

举报

举报

举报

举报

举报

举报

举报

举报