关于论坛中锁相环的问题也是不少,看来大家对这方面的研究很用心噢!今天版主分享的附件是针对集成VCO的PLL相关问题做一个问答整理,欢迎下载。

以下是版主在论坛茫茫问题中[size=18.6667px]挑选的几个[size=18.6667px]典型问题~欢迎大家跟帖一起来学习探讨哦!

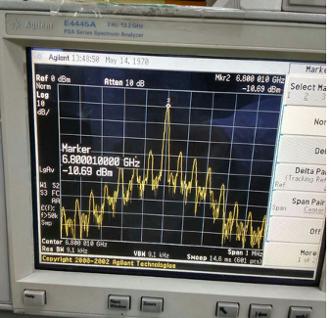

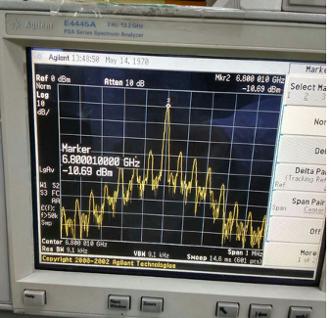

Q:使用ADF4355输出3.8GHz-6.8GHz频段内出现严重的近端杂散(1MHz带宽内),参考频率为100MHz,鉴相频率为100MHz。[size=18.6667px]杂散点间隔约70k,尝试过改变鉴相频率、改变环路滤波器带宽(ADIsimPLL软件计算得到)都没有解决该问题。电源方面:+5V供电为DC-DC电源后接LDO电源提供、+3.3V电源为LDO直接提供,感觉电源应该比较理想。具体杂散情况见如下图:

PCB板方面:去耦电容和芯片接地脚都正常接地,不过接地孔距离较远(约2mm),且很多都是盲孔到中间层的地,不是通孔到底层地,具体见图片。请指导一下有哪些可能的原因,谢谢!

A:此处是开关电源的问题,产生的70KHz叠加到主频上去了,通过增加电源滤波得到改善,相噪指标一般,还可以考虑通过配置CP current 以及 Bleed current和环路带宽来调整。主要调节寄存器R4和R6。

Q:ADF4355的小数杂散在ADIsimPLL v4.0上没有显示,试过ADF5355也没有。能否给出小数杂散的最差值?例如分子为1,分子为2,分子为2^23;分子/2^24为1/3,分子/2^24为1/4,分子/2^24为1/5,分子/2^24为1/10?现在计算到小数部分(分子/2^24)在0.05至0.2之间,其最差杂散能测到多少?PFD在50MHz和100MHz间选择。

A:对于固定modulus的小数PLL, 如fixed 24bit,可以忽略其小数spur,所有小数spur都被平均成噪底,应该在-90dBc以下。

Q:ADF4355/5355为何锁定如此慢??ADF4351的锁定时间是100us数量级的。到了ADF4355及5355,为何忽然就变成2ms数量级了?而且不论多大的环路带宽,2ms都还不能算是“稳定”的锁定,有很大概率锁不上。仿真软件里面,关闭VCO的自动ADJ,速度可以快上去——但是手册中明确说了扫频工作不能关闭。实际测试,关了以后无输出。请问,这东西真的只能这么慢吗?

A:ADF4355/5355为超宽带的PLL/VCO,里面集成256个子band,如手册描述,VCO自校准选band的时间比较长,但是你可以采用手动选band的模式,可以大大减少锁定时间,手动选band的操作见附件。

Q:如果需要做一个全景扫频应用,例如,Step=1KHz,那么就需要存储非常多的点,这会导致较高的存储成本。如果Step继续减小或将来的应用可能出现不在表中的频率,则很不现实。能否这样:

PCB板方面:去耦电容和芯片接地脚都正常接地,不过接地孔距离较远(约2mm),且很多都是盲孔到中间层的地,不是通孔到底层地,具体见图片。请指导一下有哪些可能的原因,谢谢!

A:此处是开关电源的问题,产生的70KHz叠加到主频上去了,通过增加电源滤波得到改善,相噪指标一般,还可以考虑通过配置CP current 以及 Bleed current和环路带宽来调整。主要调节寄存器R4和R6。

Q:ADF4355的小数杂散在ADIsimPLL v4.0上没有显示,试过ADF5355也没有。能否给出小数杂散的最差值?例如分子为1,分子为2,分子为2^23;分子/2^24为1/3,分子/2^24为1/4,分子/2^24为1/5,分子/2^24为1/10?现在计算到小数部分(分子/2^24)在0.05至0.2之间,其最差杂散能测到多少?PFD在50MHz和100MHz间选择。

A:对于固定modulus的小数PLL, 如fixed 24bit,可以忽略其小数spur,所有小数spur都被平均成噪底,应该在-90dBc以下。

Q:ADF4355/5355为何锁定如此慢??ADF4351的锁定时间是100us数量级的。到了ADF4355及5355,为何忽然就变成2ms数量级了?而且不论多大的环路带宽,2ms都还不能算是“稳定”的锁定,有很大概率锁不上。仿真软件里面,关闭VCO的自动ADJ,速度可以快上去——但是手册中明确说了扫频工作不能关闭。实际测试,关了以后无输出。请问,这东西真的只能这么慢吗?

A:ADF4355/5355为超宽带的PLL/VCO,里面集成256个子band,如手册描述,VCO自校准选band的时间比较长,但是你可以采用手动选band的模式,可以大大减少锁定时间,手动选band的操作见附件。

Q:如果需要做一个全景扫频应用,例如,Step=1KHz,那么就需要存储非常多的点,这会导致较高的存储成本。如果Step继续减小或将来的应用可能出现不在表中的频率,则很不现实。能否这样:

- 按1MHz间距存点,对于任意频率,选择距它最近的已知频率的数据。

- 设法找到有关参数变化的分界点并存储下来,以便由程序判断该输入哪个数据。

A:

- 按1MHz间距存点,对于任意频率,选择距它最近的已知频率的数据。 - 可以

- 设法找到有关参数变化的分界点并存储下来,以便由程序判断该输入哪个数据。- 可以

Q:有关的数值是否与温度或其它时变因素有关,也就是说,是不是只需要获取一次数据,就可以终身不用再次获取。是否只用关心VCO工作频率范围(3.4-6.8G),不用关心输出分频器。

A:跟温度无关,跟输出分频器也无关。

举报

举报

举报

举报

举报

举报

举报

举报